### LINK 480Z INFORMATION FILE

### PN 10939, Rev.1

# Copyright (c) 1982, 1983 by Research Machines Limited

All rights reserved. Copies of this publication may be made by customers exclusively for their own use, but otherwise no part of it may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language without the prior written permission of Research Machines Ltd., Post Office Box 75, Oxford, England. OX2 OBW Tel: Oxford (0865) 249866.

The policy of Research Machines Limited is one of continuous development and improvement of its products and services, and the right is therefore reserved to revise this document or to make changes in the products software it describes without notice. Research Machines Limited endeavour to ensure the accuracy of this document and to ensure that the products described perform correctly according to their descriptions. However, Research Machines Limited do not accept liability for the consequences of any error or omission.

Additional copies of this publication may be ordered from Research Machines Limited at the address above. Please ask for the 'LINK 480Z Information File, PN 10939'.

### Reader's Comments

To assist Research Machines to improve the quality of its technical publications and its computer and software products we would like to hear from users on their experience with using them.

Comments referring to this manual should include:

- o a description of any errors you have found

- comments on problems you have encountered with understanding and using the manual, and suggestions for improvement

- your name and address and a brief description of your experience with using microcomputer systems

Queries about this manual should be sent to:

The Technical Publications Department, Research Machines Limited, PO Box 75, Oxford. OX2 0BW

Reports referring to difficulties in using any of the products described in this manual should include:

- o a written description of each step taken and each key or command you have used

- o details of the hardware configuration, and the version numbers of the software in use

- o the nature of the error

and should be sent to:

Technical Support Department, Research Machines Limited, PO Box 75, Oxford. OX2 0BW

### CONTENTS

| CHAPTER | 1: | INTRODUCTION                       | 1.1  |

|---------|----|------------------------------------|------|

|         |    | LINK 480Z Documentation            | 1.1  |

|         |    | The LINK 480Z Information File     | 1.1  |

| CHAPTER | 2: | HARDWARE SPECIFICATION             | 2.1  |

| CHAPTER | 3: | PERIPHERAL INTERFACES              | 3.1  |

|         |    | Cassette Interface                 | 3.1  |

|         |    | Use of Cassette Interface          | 3.1  |

|         |    | Cassette Filing System             | 3.1  |

|         |    | General Principles                 | 3.1  |

|         |    | File Structure                     | 3.2  |

|         |    | Device and File Specification      | 3.3  |

|         |    | File Format                        | 3.3  |

|         |    | Cassette Hardware                  | 3.4  |

|         |    | Output to Cassette                 | 3.4  |

|         |    | Input from Cassette                | 3.4  |

|         |    | Cassette Recorder Motor Control    | 3.4  |

|         |    | Serial Interfaces                  | 3.5  |

|         |    | Driving a Serial Interface (SIO-4) | 3.6  |

|         |    | Parallel Interface                 | 3.7  |

|         |    | Comparison with 380Z User I/O Port | 3.8  |

|         |    | Example of use                     | 3.8  |

|         |    | Beeper                             | 3.8  |

|         |    | Analogue Output                    | 3.9  |

|         |    | Accessories                        | 3.9  |

|         |    | Switches                           | 3.9  |

|         |    | Connection Information             | 3.11 |

| CHAPTER | 4: | HIGH RESOLUTION GRAPHICS           | 4.1  |

|         |    | General Information                | 4.1  |

|         |    | Resolutions                        | 4.1  |

|         |    | Look-up Table                      | 4.2  |

|         |    | Colour                             | 4.2  |

|         |    | Video Outputs                      | 4.2  |

|         |    | Detailed Information               | 4.3  |

|         |    | Selection of Operating Mode        | 4.4  |

|         |    | Accessing the Screen Memory        | 4.4  |

|         |    | Calculation of the Byte Address    | 4.5  |

|         |    | Mask Generation                    | 4.5  |

|         |    | Modifying Screen RAM               | 4.5  |

|         |    | Accessing the Look-up Table        | 4.6  |

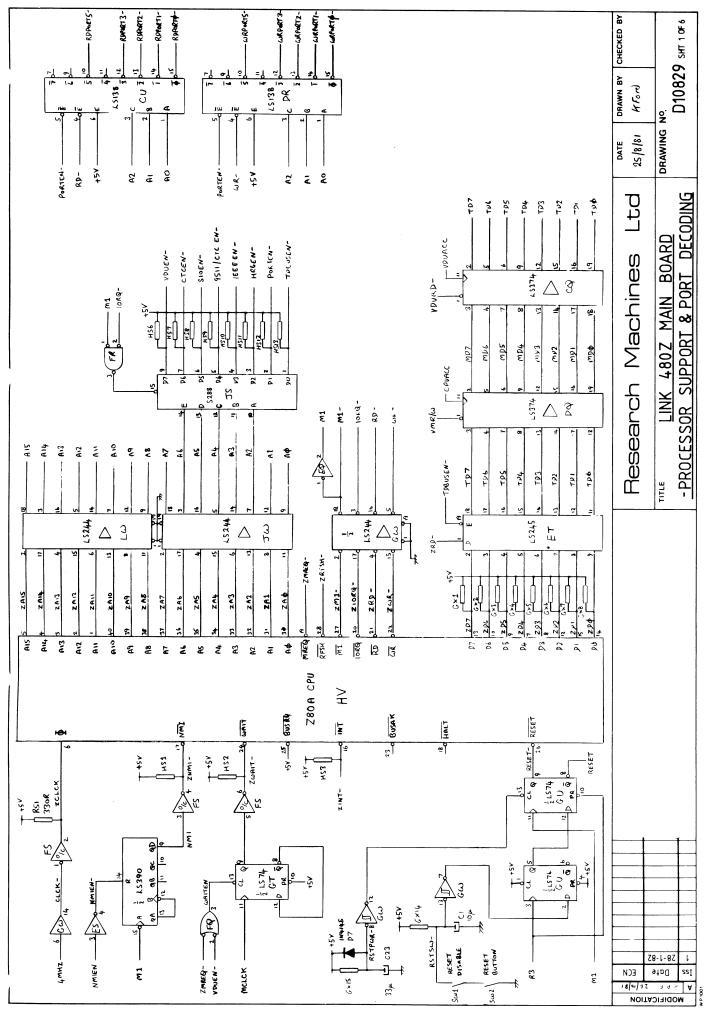

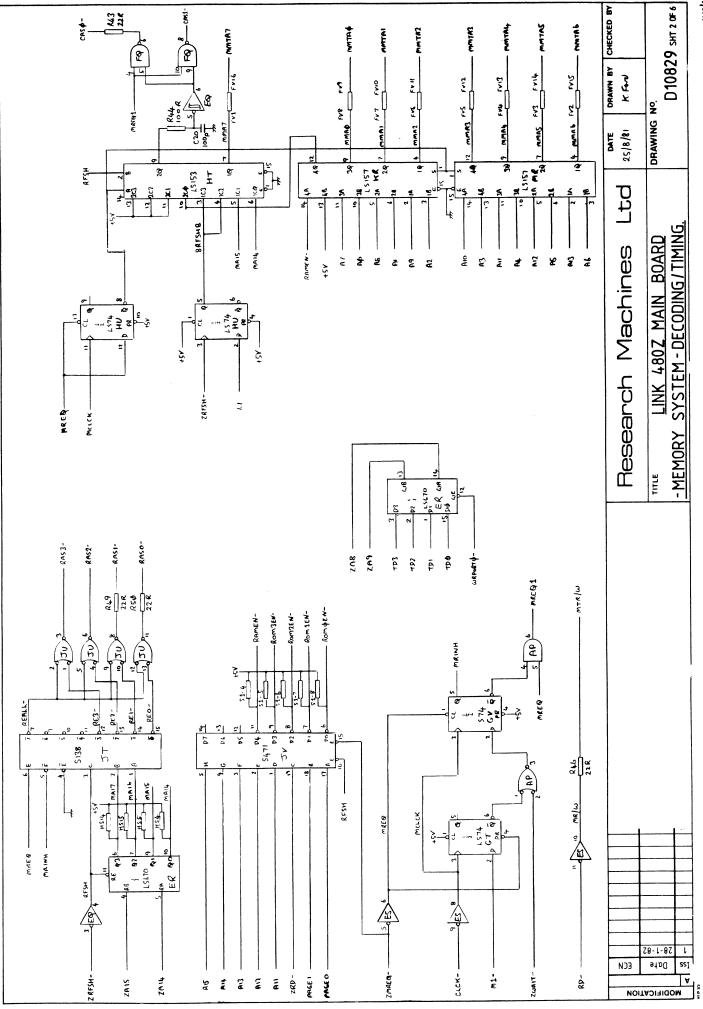

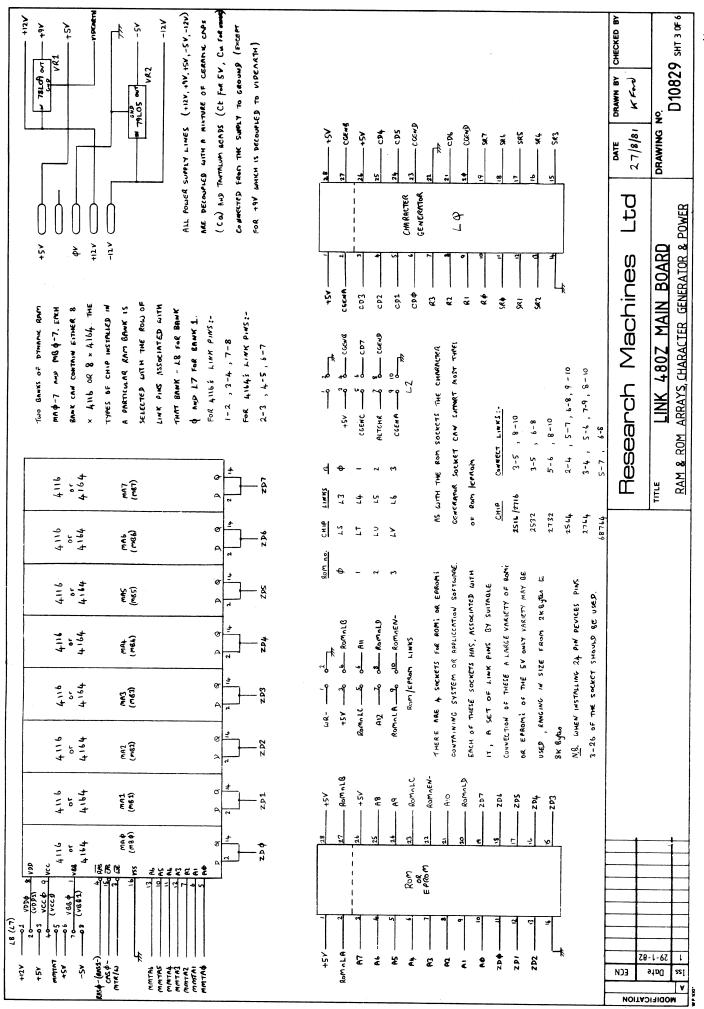

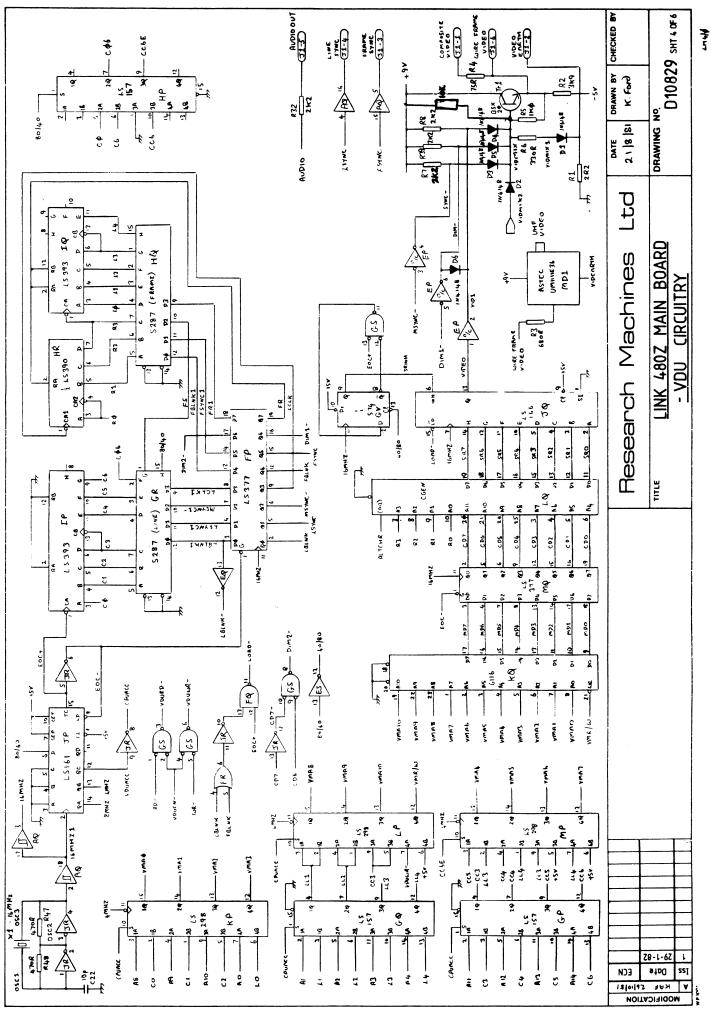

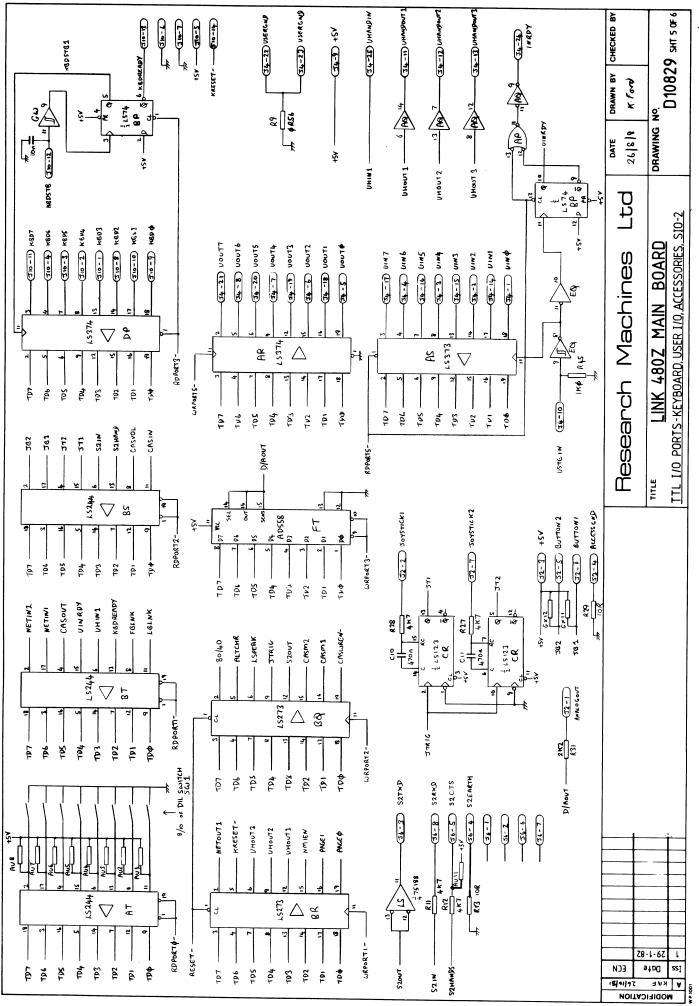

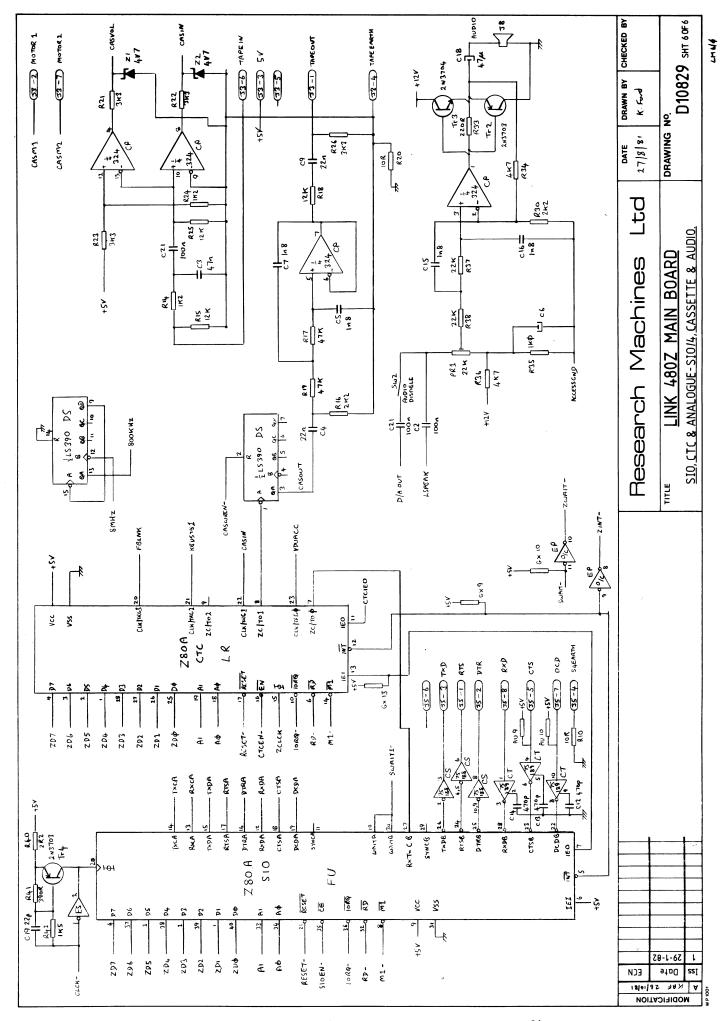

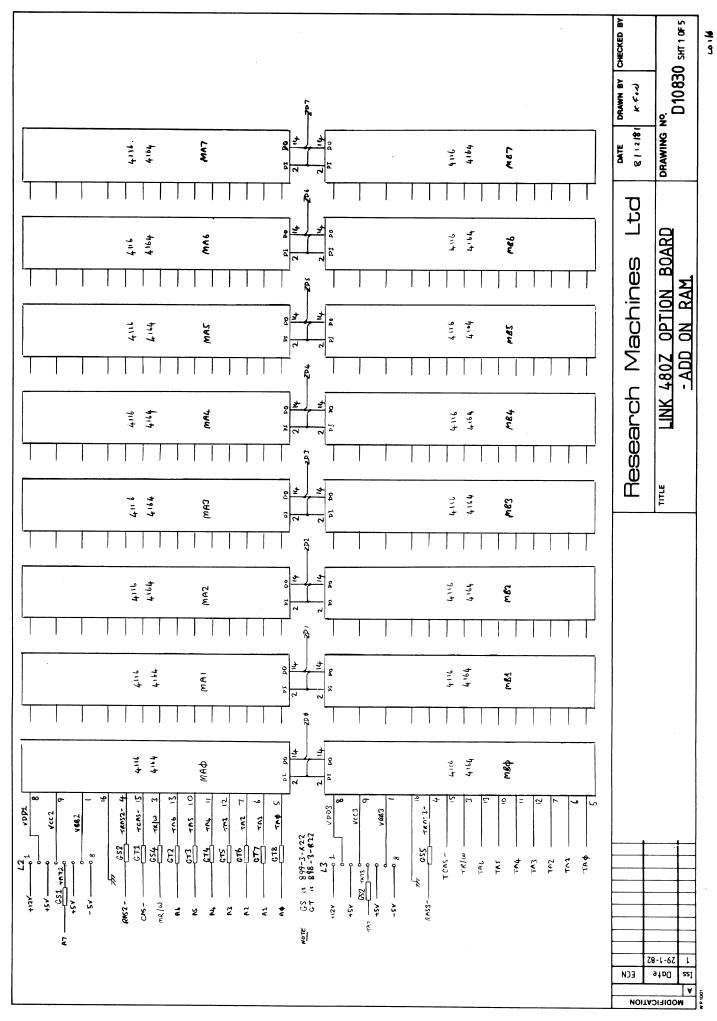

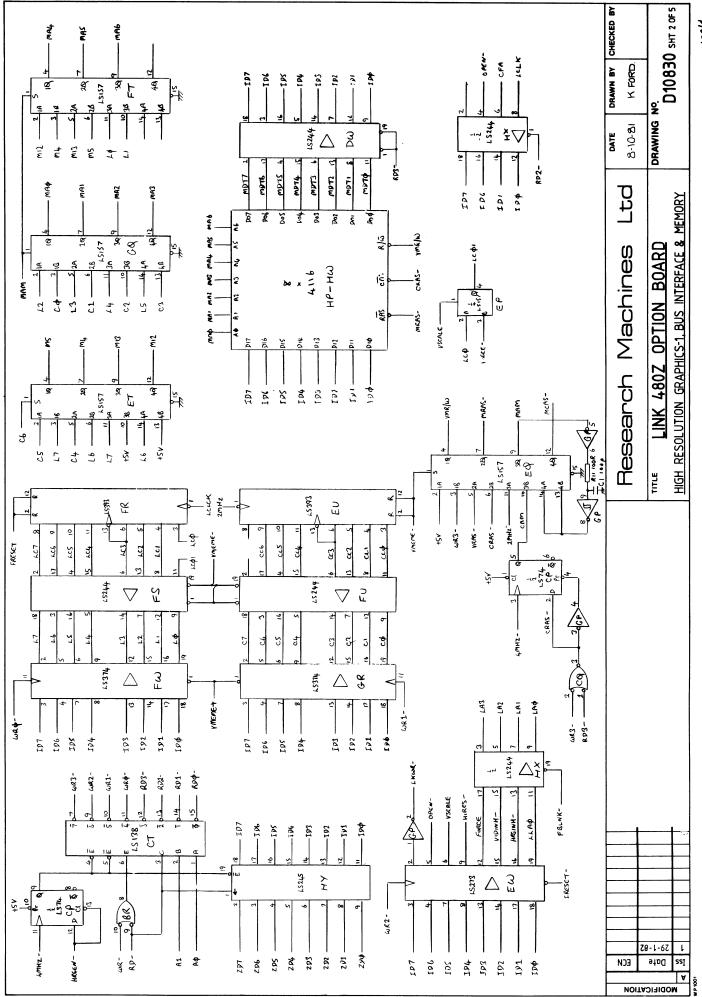

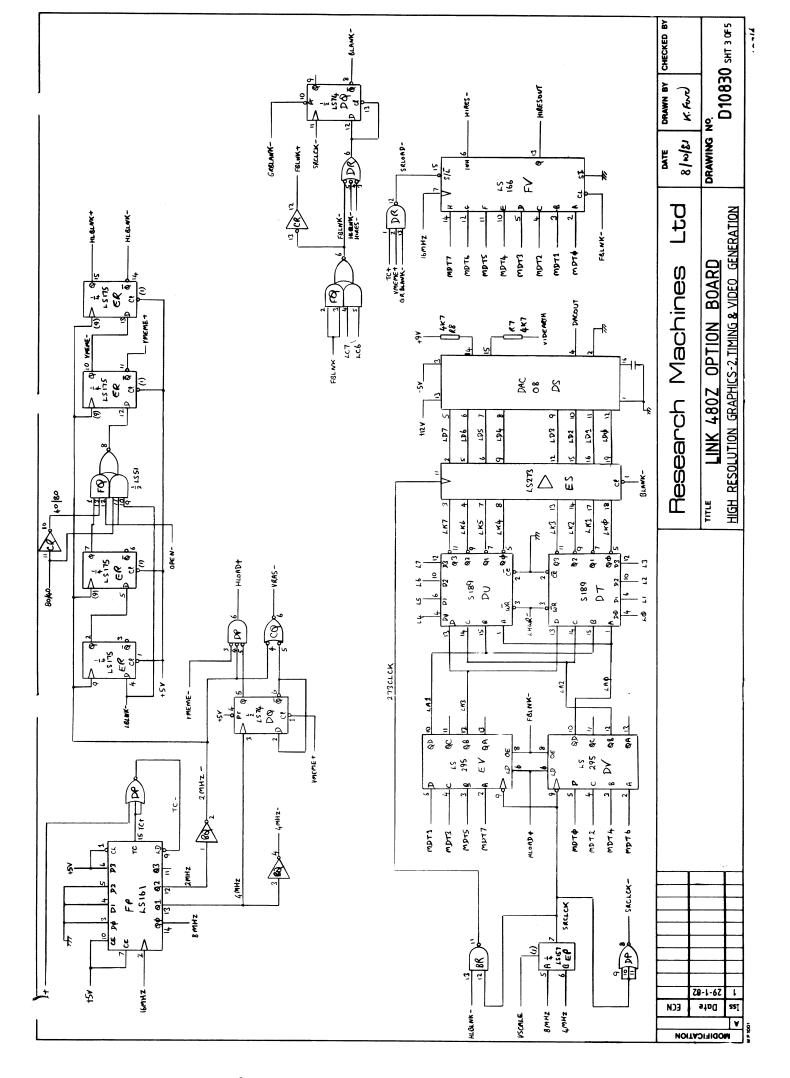

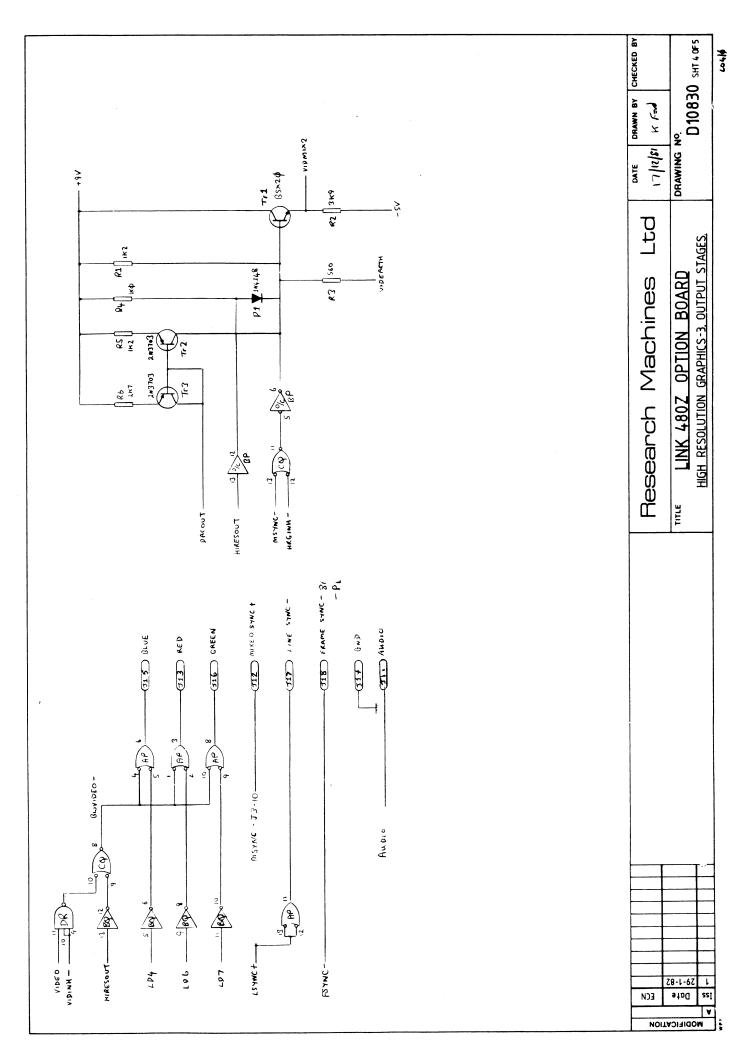

APPENDIX B: Circuit Diagrams

в.1

| Controlling the Video Outputs<br>Colour Graphics<br>Opening the Screen | 4.8<br>4.8<br>4.9 |

|------------------------------------------------------------------------|-------------------|

| CHAPTER 5: HARDWARE NOTES                                              | 5.1               |

| Memory Maps                                                            | 5.1               |

| 64K Byte System                                                        | 5.2               |

| Ports                                                                  | 5.3               |

| Control/Status Ports                                                   | 5.4               |

| HRG Control Ports                                                      | 5.6               |

| Interrupt Priorities                                                   | 5.7               |

| CTC Usage - Main Board                                                 | 5.8               |

| General                                                                | 5.8               |

| Channel 0                                                              | 5.8               |

| Channel 1                                                              | 5.8               |

| Channel 2                                                              | 5.9               |

| Channel 3                                                              | 5.9               |

| Limitations Imposed by the CTC Us                                      | age 5.9           |

| CTC Usage - Option Board                                               | 5.9               |

| General                                                                | 5.9               |

| Channel 0                                                              | 5.10              |

| Channel 1                                                              | 5.10              |

| Channel 2                                                              | 5.10              |

| Channel 3                                                              | 5.10              |

| Keyboard Interface                                                     | 5.11              |

| Video Display                                                          | 5.11              |

| APPENDIX A: Character Sets                                             | A.1               |

| INDEX | I.1 |

|-------|-----|

### CHAPTER 1

### INTRODUCTION

#### LINK 480Z MANUALS

The following manuals are provided by Research Machines to help you set up and use a LINK 480Z:

- LINK 480Z User Guide: this manual explains how to set up and use your system and its facilities.

- Programming Manuals: each item of software that you purchase is supported by one or more manuals which explain how to set up and use the software provided.

#### THE LINK 480Z INFORMATION FILE

This manual contains technical specifications of various features of the 480Z hardware including for example, the various interfaces that are supported by the 480Z.

Chapter 2 gives an overall description of the 480Z hardware. Chapter 3 describes the various interfaces which are available on the 480Z. Chapter 4 provides a description of the hardware aspects of the high resolution graphics facilities, and Chapter 5 describes the other hardware in greater detail.

### CHAPTER 2

# HARDWARE SPECIFICATION

# LINK 480Z - SPECIFICATION

| Processor:        | Z80A 4MHz                                                                                                                                                                        |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Memory:           | 64K (58K user)RAM. 8K ROM monitor (ROS).<br>20K BASIC in ROM. 4K Network firmware.                                                                                               |  |  |

| Keyboard:         | 65 Key with n-key rollover. Includes 4 cursor control<br>keys and 4 special function keys (all 8 of which are<br>user-definable), upper/lower case, caps lock and<br>repeat key. |  |  |

| Display:          | 40-character by 24-row, or optional 80-column mode, software selectable down to 40-column mode.                                                                                  |  |  |

|                   | 128-character set plus 80 x 72 or 160 x 72 low-<br>resolution graphics in two shades of grey.                                                                                    |  |  |

|                   | Video and UHF outputs are provided.                                                                                                                                              |  |  |

| External storage: | 1200 bps and 300 bps cassette interface, optional external dual cassette controller.                                                                                             |  |  |

| Tone generation:  | Miniature internal loudspeaker driven by an optional<br>digital to analogue converter. Also simple 'beep'<br>facility. Internal volume control/disable.                          |  |  |

| Reset button:     | On rear panel - can be disabled internally.                                                                                                                                      |  |  |

| Input/Output      |                                                                                                                                                                                  |  |  |

| Parallel I/O:     | One 8-bit parallel input/output port with 4 line<br>strobe and acknowledge lines. Also suitable for<br>driving Centronics standard parallel printers.                            |  |  |

| Serial I/O:       | Three serial interfaces fitted as standard.                                                                                                                                      |  |  |

|                   | 1. Low speed 110-2400 baud with busy line.                                                                                                                                       |  |  |

|                   | <ol> <li>High speed 110-9600 baud with full 4-wire<br/>handshake.</li> </ol>                                                                                                     |  |  |

|                   | <ol> <li>Synchronous 800k bps serial interface for<br/>network operation. (Needs network transceiver<br/>for connection to the network cable.)</li> </ol>                        |  |  |

| Paddle and pushbutton input:   | DIN socket which can be used to determine the position of two paddles (or a joystick) and two pushbuttons.                                   |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Analogue output:<br>(Optional) | User can link output internally to produce beep only.<br>Digital to analogue converter is then available<br>externally on rear panel socket. |

| ROM:                           | ROM expansion sockets are available which will allow for expansion.                                                                          |

Option Board

Graphics: • Three major modes: 640 x 192 monochrome 320 x 192, 4 colours per point 160 x 96, 8 colours or 16 shades of grey per point (2 pages)

- Software definable colour look-up table

- Video output, UHF output and TTL RGB output

- Graphics and text output may be displayed separately or be superimposed under software control

- The Graphics memory is separate from CPU RAM, so the full address range of the CPU may be used

### Plug-in options

CTC: Real-time clock and interrupt controller

Hardware Floating point (Maths Chip) (Under development): Plug-in hardware floating point option.

# Further Expansion of

System

- 256K bytes of RAM: Use of 64K RAMs enables the user to have 256K of RAM. The user-visible RAM is 58K bytes (out of 64K). The remaining 192K is available as backing data store.

- Network Operation: To connect to a Research Machines network, a transceiver unit is needed to connect to the network cable. To fit this unit, the 480Z must be returned to Research Machines Ltd.

### Rear Panel Connections and Controls

# i) Basic system row:

| Туре              | Function                                                        |

|-------------------|-----------------------------------------------------------------|

| Phono             | UHF out                                                         |

| Push button       | Reset                                                           |

| 6-way DIN         | Video out                                                       |

| 7-way DIN         | Accessory socket, paddles, push buttons, D/A analogue<br>output |

| 7-way DIN         | Cassette I/O                                                    |

| 25-way D type     | Parallel I/O (User I/O)                                         |

| 8-way DIN         | RS232 interface (SIO-2)                                         |

| 8-way DIN         | RS232 interface (SIO-4)                                         |

| 10-way DIL switch | Network address, reset disable, loudspeaker disable             |

| BNC*              | Internal network transceiver                                    |

|                   |                                                                 |

\*only active if option installed

ii) Option Board row\*:

8-way DIN\* Colour TTL Red, Green, Blue output

\*only active if option installed

### General:

Power consumption 30 Watts, approximately. Dimensions Width 532mm Depth 331mm Height 95mm

### CHAPTER 3

### PERIPHERAL INTERFACES

#### CASSETTE INTERFACE

### Use of Cassette Interface

The cassette recorder interface circuits comprise a tone generator with a band pass filtered output which is capable of generating approximately sinusoidal waveforms at frequencies in the range ca. 1200Hz to 2400Hz and also some input shaping and filtering circuits which allow the frequency and phase of the incoming signal to be determined. There are also two output lines which are used to control a dual cassette controller, thus allowing the computer to control the cassette recorder motors.

The cassette system is capable of operating in two different modes. In slow mode the data transfer rate is nominally 300 baud while in fast mode the transfer rate is nominally 1200 baud. All cassette tapes supplied by Research Machines are now recorded in fast mode to increase the speed of loading and saving programs.

In slow mode a logic '1' is recorded as 8 cycles of 2400Hz while a '0' is recorded as 4 cycles of 1200Hz. In fast mode a '1' is 2 cycles of 2400Hz while a '0' is 1 cycle of 1200Hz.

Each byte is recorded on the tape with one start bit (a '0') followed by 8 data bits (least-significant bit first) and two stop bits (recorded as 1's). Any gap between bytes will be recorded at 2400Hz and so will behave as a continuation of the stop bits of the previous byte.

Note that although the frequencies used are nominally 1200Hz and 2400Hz, they are actually about 1115Hz and 2230Hz. This is in order to provide compatibility with the 380Z.

### Cassette Filing System

### General Principles

The Cassette Filing System (CFS) supplied with the cassette-based 480Z systems, for example as part of cassette BASIC, provides the user with a set of facilities to control input from, and output to, files recorded on cassettes. The system takes care of all data transfers to or from cassette, handles all the necessary packing or unpacking of blocks of data, and detects and reports errors.

File Structure

A CFS file consists of a number of blocks. Each block holds the name of the file, the block number, and the data. A checksum is also included.

The block layout is:

| Byte 0:          | SYN                      |

|------------------|--------------------------|

| Bytes 1-10:      | Name of file             |

| Byte 11:         | BLKH                     |

| Byte 12:         | BLKL                     |

| Byte 13:         | Length of Data Block = n |

| Bytes 14-(n+13): | Data (0-255 bytes)       |

| Byte n+14:       | Checksum                 |

The SYN character (16 hex, 22 decimal) allows accurate synchronization when reading the tape.

The name of a file comprises 1-6 characters for the primary name, optionally followed by a full stop and 1-3 further characters for the extension. The characters should be drawn from the sets A-Z, 0-9, and \$. It is recommended that programs should convert any lower case letters to upper case before writing the block. If the primary name and extension are shorter than 6 or 3 characters respectively, they must be padded with spaces.

BLKH and BLKL are the high and low bytes of the block number. Note the order of these two bytes. The first block of a file is numbered zero.

The Length of Data Block field is self-explanatory. A zero-length block represents the end of a file.

The checksum is calculated by adding together all of the bytes in the record apart from the SYN character (and the checksum!), negating, and reducing modulo 256. This means that, on reading, all the bytes apart from the SYN character should be added together, and the result should be zero (modulo 256) if the block is not corrupt.

When a file is recorded, it is usually safest to record more than one copy of each block. Copies of a block should be separated by at least 200 ms. Different blocks should be separated by at least 2 seconds of '1' tone if the tape is to be read by general-purposeprograms. Specialist applications may get away with reducing this gap. Standard practice is to use two copies of each block.

Normal practice is to turn on the appropriate cassette relay bit just before reading or writing a block, and to turn it off immediately after completing the operation. If multiple copies of a block are being written, the bit should be reset only after writing the last copy. These measures allow the use of the Dual Cassette Controller.

There is no restriction on the data which may be recorded in a cassette file. However, most programs regard CTRL/Z (1A hex, 26 decimal) as an end-

of-file marker, so this character should be avoided if possible.

Device and File Specification

When CFS is requested to open a device or file for reading or writing, it requires a file specification of the following form:

dev:filename.ext

where dev: represents the characters specifying the device name. CFS recognises 5 devices:

| Display and keyboard         | CON: |

|------------------------------|------|

| Tape out or paper-tape punch | PUN: |

| Tape in or paper-tape reader | RDR: |

| Line printer                 | LST: |

| Cassette file                | CAS: |

If there is no colon present then a cassette file, CAS:, is assumed by default.

- Filename represents the name, up to six alphanumeric characters long, of the file on the given device which is to be opened. A file name is required ONLY if the device name is CAS:

- ext represents an extension, or file type, of up to 3 alphanumeric characters. If this is omitted, a blank extension will be assumed by default. If the extension is omitted, the period may be omitted also.

### File Format

When outputting a file, CFS normally writes two copies of each block of the file to tape.

When CFS is inputting a file it starts the cassette recorder and looks for an interblock gap and a block header. The file name and block number of any block header found are displayed on the console usually on the bottom line of the screen. Automatic paging is disabled. CFS keeps reading blocks until it finds a block header which matches the block it is looking for. CFS then reads the block into its input buffer. If a checksum error is detected, then CFS indicates a soft error by showing an arrow ( >) in front of the filename displayed on the screen, and then tries to read a later copy of the same block from the tape. If CFS exhausts the copies of the block, without having read an error free copy, it returns to the user's program with a hard error indication. It is then the responsibility of the user's program to decide what action to take.

### Cassette Hardware

Output to Cassette

The output signal is generated by one channel of the Z80 CTC on the 480Z main board. The output from the CTC is actually in the form of a train of very short pulses. This passes through a stage which converts it to a square wave of half the frequency. This is then passed through an analogue band pass filter in order to produce a closer approximation to a sine wave output. This signal is then fed to the output socket at a low level, suitable for feeding into the microphone socket of a tape recorder.

Because the output frequency is generated by a CTC any changes of the output frequency will be neatly synchronised by the CTC itself and hence there is no necessity for the processor to synchronise the transitions itself. However because the output of the CTC is connected to a divide-bytwo stage the phase of the output signal will not be known. This problem is overcome by allowing the processor to read the output of the divide-bytwo stage.

### Input from Cassette

The signal from the cassette recorder on play-back should be at a high level (ca. 1.5V rms) and will normally be taken either from the recorder DIN connector or from an external loudspeaker or earphone socket. After shaping and filtering this signal can then be read by the processor as two bits (0 and 1) in status port 2. Bit 1 of this port is the volume bit and is used for setting the playback volume of the recorder. The volume is correct when there are occasional transitions of this bit from high (its normal state) to low. Bit 0 of the port is the signal from which information is actually recovered. This line is also connected to one of the inputs of the CTC so that an interrupt can be generated on transitions.

The input data is decoded by measuring the time between successive edges of the same polarity and hence determining whether the intervening cycle was 1200Hz or 2400Hz. If the tape being read was in slow mode then there are several such cycles for each bit and a degree of signal averaging is performed on the cycles to provide extra noise immunity and protection from drop-outs etc. In fast mode these protections are not possible and this is the major cause of the lower reliability of fast mode.

It is important that the polarity of the input signal is correct since otherwise, whenever a transition occurs, a cycle consisting of 1/2 cycle at 1200Hz and 1/2 cycle at 2400Hz will be measured. If this occurs in slow mode then signal processing will cope with the problem and the only effect will be to lower reliability. However in fast mode the system will cease to work at all. Thus it is important that the cassette recorder used should have no phase inversion between its input and its output. All cassette recorders provided by Research Machines Limited will satisfy this requirement.

#### Cassette Recorder Motor Control

Bit 1 and 2 of control port 2 are used to control the cassette recorder

motors. By convention bit 1 controls recorder 1 which is connected for reading (replay) while bit 2 is used for recorder 2 which is used for writing (record). Separating the read and write functions in this way simplifies the actions required of the user (and the software). If no dual cassette controller is being used then one cassette recorder provides both read and write functions with no motor control. If, however, a dual cassette controller is being used but is switched to 'single' mode then only one cassette recorder is necessary but the computer still has motor control.

### SERIAL INTERFACES

The 480Z has two RS232 serial interface ports, the SIO-2 and the SIO-4, the names being chosen for compatibility with the 380Z.

The SIO-4 is a high speed bi-directional interface (up to 9600 baud) with full modem handshake and is implemented using channel B of the Z80 SIO chip. ROS supplies sufficient software to allow for its use as an input, output or bi-directional port, the only limitation being that send and receive baud rates must be the same.

The SIO-2, on the other hand, is implemented in software and so is rather slower than the SIO-4, maximum 2400 baud. ROS supports the use of the SIO-2 as an output device (e.g. for driving a printer) but not as an input device. The SIO-2 has a single input handshake line which is intended to be connected to a printer "READY" line. It is equivalent to the CTS line on the SIO-4 (see below).

The baud rates available for these SIOs are:

| 110  | baud | - | baud | code | 0 |        |       |

|------|------|---|------|------|---|--------|-------|

| 300  | baud | - | baud | code | 1 |        |       |

| 600  | baud | - | baud | code | 2 |        |       |

| 1200 | baud | - | baud | code | 3 |        |       |

| 2400 | baud | - | baud | code | 4 |        |       |

| 4800 | baud | - | baud | code | 5 | (SIO-4 | only) |

| 9600 | baud | - | baud | code | 6 | (SIO-4 | only) |

The baud rates may be set up by means of the BASIC PRINTER command, ROS O command or by a call to EMT SETLST with the printer code (2 for the SIO-2, 4 for the SIO-4) in A and the baud code, defined above, in register E. This call also has the effect of setting EMT LPOUT's transfer vector to the appropriate driver routine. Thus if, for example, it is desired to use the SIO-2 for a printer and the SIO-4 for some other purpose then the SIO-4 baud rate should be set by a call to SETLST prior to setting up the SIO-2 by a second call to SETLST.

The SIO-4 supports the following handshake lines: CTS, DCD (also known as DSR), RTS, and DTR. The function of each of these lines is described briefly overleaf.

- CTS (Clear To Send) is an input to the 480Z. It functions as a transmitter enable. Thus the SIO-4 will not transmit any data unless this line is active. It thus serves as a printer "READY" line since no characters will be sent until the printer is ready.

- DCD (Data Carrier Detect) or DSR (Data Set Ready) is an input to the 480Z. It functions as a receiver enable line. Thus the SIO-4 will ignore all input data unless this line is active.

- RTS (Request To Send) is an output from the 480Z. This line is intended to indicate to the peripheral that the 480Z has a character or characters ready for transmission. Thus if two 480Zs were to be connected via their SIO-4s this line would be connected to the DCD line on the other machine.

- DTR (Data Terminal Ready) is an output from the 480Z. The line goes active when the 480Z is ready to receive a byte and goes inactive when the SIO-4's receive buffer becomes full. Thus this line functions in the same way as a printer's "READY" line.

It should be noted that the CTS and DCD pins have pull-up resistors connected to them so that if nothing is connected to them they float into the active state and thus allow the transmitter and receiver to function correctly.

### Driving a Serial Interface (SIO-4)

Terminal mode software for the 480Z (fully position independent) is coded in ROS 1.1 and later versions and is activated using the ROS command T:

| T480:  | EMT<br>JR<br>EMT<br>EMT       | KBDTL<br>Z, T480A<br>KBDW<br>LPOUT        | ; is there a character on the keyboard?<br>; jump if not<br>; else get the character<br>; and output it              |

|--------|-------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| T480A: | EMT<br>JR<br>EMT<br>EMT<br>JR | S4KTL<br>Z, T480<br>S4KIN<br>OUTC<br>T480 | <pre>; is there a character on the input line? ; jump if not ; else get the character ; display it ; and loop.</pre> |

| KBDTL  | EQU                           | 31                                        |                                                                                                                      |

| KBDW   | EQU                           | 33                                        |                                                                                                                      |

| LPOUT  | EQU                           | 5                                         |                                                                                                                      |

| S4KTL  | EQU                           | 47                                        |                                                                                                                      |

| S4KIN  | EQU                           | 48                                        |                                                                                                                      |

| OUTC   | EQU                           | 1                                         |                                                                                                                      |

### PARALLEL INTERFACE

The basic 480Z has an 8-bit parallel interface known as the User I/O port. This port is mapped as a Z80 input/output port at I/O address 1DH. Reading a byte from this address, for example with the instruction 'IN A,(1DH)', causes the input data to be read. Outputting a data byte using the instruction 'OUT (1DH),A' results in that byte being latched on the User I/O output lines.

The port will, typically, be used for driving a parallel printer, possibly of the 'Centronics' variety. However the port may also be used to drive simple home-built interfaces. For this purpose a +5V power supply is available on the connector. Only low currents should be drawn from this pin however.

In normal use any data written to port 1DH appears latched on the output lines and an input from port 1DH results in a read of the current state of the input lines. However in order to allow for interface to devices having handshake lines there are also some extra handshake pins on the connector.

There is an input strobe line on the connector. While this line is at logic '0' (it will float to logic '0' if left disconnected) the data read by an input instruction will be the data currently on the input pins. However if the strobe line is taken high then the data on the input lines at that time will be latched and all subsequent reads of the input port (until the strobe is again taken low) will read the latched data. Taking the strobe line high also causes the user I/O ready line to go to a logic '0' thus indicating to the peripheral that the computer is no longer ready to accept input data. This line goes back to a logic '1' (i.e. ready) when the computer reads the user I/O port. There is also a ready line which can be read by the computer. This, however, is of the opposite sense. Thus if the bit is a logic '1' then there is a data byte latched into the user I/O input port ready to be read.

In addition to the above 'hardware' handshake lines there are also three spare uncommitted output pins and one uncommitted input pin which can be used for handshaking purposes (or as extra data bits etc.).

All of the user I/O handshake lines are in port 19H. If the uncommitted output lines are used it is important to set the remaining bits of the port according to the value in the mask which ROS maintains at location OFF01H. Furthermore, this mask should be updated with the new value output. Failure to utilise and maintain this mask will result in unpredictable operation and almost certainly will 'crash' the machine.

All input lines on the user I/O connector are Schmitt-triggered low-power Schottky devices. The strobe input is also connected to a 1k resistor whose other end is connected to ground. All output lines on the user I/O connector are driven by low-power Schottky buffer chips (74LS374 and 74LS244). For more information on these chips see the appropriate data sheets.

### Comparison with 380Z User I/O Port

The 480Z User I/O port is similar in external appearance to the User I/O port on the 380Z. However, it is an I/O mapped port rather than a memory mapped port. It is mapped as I/O port 1D hexadecimal for both input and output. Like the memory mapped port a mask must be kept for the output byte. This is now kept at FF00 hexadecimal.

The pin-out of the User I/O port remains the same as the 380Z for the 8 bits in, the 8 bits out, the +5V line, and the 0V line. The -12V and +12V lines are not available.

It should be noted that software serial interface (serial I/O 2) is not connected to the User I/O port, unlike the 380Z SIO-2.

### Example of use

To set bit 3 of the output of the User port high the following code is appropriate:

| UMASK | EQU        | 0FF00H |

|-------|------------|--------|

| UPORT | EQU        | 1DH    |

|       |            |        |

| LD    | A,(UMASK)  |        |

| SET   | 3,A        |        |

| LD    | (UMASK),A  |        |

| OUT   | (UPORT), A |        |

|       |            |        |

The equivalent BASIC code is:

| 10 | UM = &FF00    |

|----|---------------|

| 20 | UP = &1D      |

| 30 | A = PEEK (UM) |

| 40 | A = (A OR 8)  |

| 50 | POKE UM,A     |

| 60 | OUT UP,A      |

### BEEPER

The 480Z is capable of producing noises in two ways. Firstly there is a single bit in a port which is connected to the audio amplifier and can be used for producing single tones. This is the method used by ROS to generate beeps. There is an escape sequence that permits user programs to set the tone and duration of this beep. This beep cannot be disabled externally.

The second way is by using optional analogue output, as described overleaf.

### ANALOGUE OUTPUT

To produce an analogue output, an 8-bit value, N, should be written to control port 3 (1BH). The output produced is approximately N\*10 millivolts. Thus the range of the output is from 0 to 2.55 volts, approximately.

The digital to analogue converter is also connected to the audio amplifier and can be used to produce reasonable approximations to a sine wave, or indeed any waveform. However in order that the digital to analogue converter may also be used to produce an analogue output (available on the accessories socket) without making a noise in the process this output may be disconnected from the audio amplifier by setting the speaker disable switch to the up position. It should be noted that there is no software in ROS to support the use of the digital to analogue converter.

### ACCESSORIES

Provision has been made on the 480Z for the connection of an external unit containing a joystick (or two paddles) and two push buttons. Initially, Research Machines are not providing such an accessories unit, or any software to support its use.

Changing bit 4 of control port 2 (1AH) from 0 to 1 triggers two monostables. The joystick or paddles contain potentiometers which affect the width of the pulse generated. This is approximately 1 millisecond + r\*0.2 millisecond where r is the resistance in kOhms. The outputs of the monostables can be read from bits 4 and 5 of status port 2 (1AH).

The two push-buttons are assumed to provide low outputs when pressed. These can be sensed via bits 6 and 7 of status port 2 (1AH).

#### SWITCHES

The basic 480Z has externally accessible switches for the following purposes:-

Reset disable (R) Speaker disable (S) Network address (NET ADDR)

They are accessible through a hole in the rear panel, and their position may be changed using a small screwdriver, for example:

R: Reset Disable Switch: when this switch is in the up position the rear panel reset button of the 480Z is disabled. Under these conditions there is no way of resetting the machine without re-enabling the reset disable switch.

- S: Speaker Disable Switch: when this switch is in the up position the output of the digital-to-analogue converter is disconnected from the audio amplifier. It does not disable the 'beep' which can be produced by ROS.

- NET ADDR: Network Address Switches: these 8 switches are to be used to set the station address for a 480Z on a network. Switches are arranged with the least significant address bit at the right-hand end when viewed through the rear panel. A switch in the up position corresponds to a 1. Details of setting up network addresses will be found in the Network Manager's Guide.

### CONNECTION INFORMATION

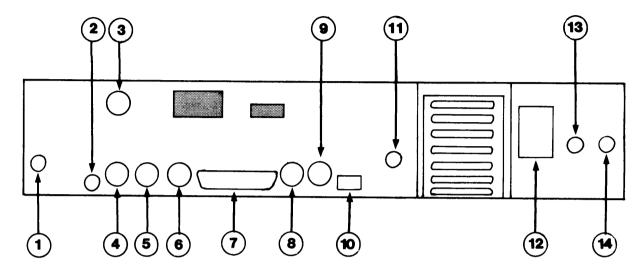

The layout of the sockets, switches and mains cables on the rear panel of the LINK 480Z is shown in the diagram below.

Connection Information

| 1.  | Modulator UHF (TV)            |      |

|-----|-------------------------------|------|

| 2.  | RESET button                  |      |

| З.  | TTL RGB                       |      |

| 4.  | Video                         | (A)  |

| 5.  | Accessories                   | (B)  |

| 6.  | Cassette                      | (C)  |

| 7.  | Parallel I/O                  | (D)  |

| 8.  | Serial I/O 4                  | (E)  |

| 9.  | Serial I/O 2                  | (F)  |

| 10. | Network Address, Speaker, and |      |

|     | Reset Disable Switches        | 3.10 |

| 11. | Network Interface Coaxial     |      |

| 12. | Mains ON/OFF                  |      |

- 12. Mains ON/OFF

- 13. Fuse

- 14. Mains Cable

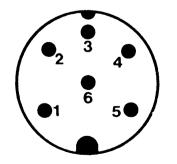

### (A) VIDEO SOCKET

6-PIN DIN SOCKET POSITION 4\*

- (1) VIDEO SIGNAL(2) GROUND

- (3) FRAME SYNC

- (4) LINE SYNC

- (5) AUDIO OUT

- (6) WIREFRAME VIDEO

WIRE FRAME VIDEO MONITORS ONLY

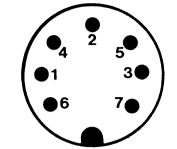

- (B) ACCESSORIES SOCKET 7-PIN DIN SOCKET POSITION 5\*

- (1) ANALOGUE OUTPUT

- (2) JOYSTICK 1

- (3) +5V

- (4) GROUND

- (5) BUTTON 1

- (6) BUTTON 2

- (7) JOYSTICK 2

- • • • • • • •

(C) CASSETTE PORT

7-PIN DIN SOCKET POSITION 6\*

- (1) SIGNAL FROM COMPUTER TO CASSETTE RECORDER

- (2) RECORDER 1 MOTOR CONTROL

- (3) +5V

- (4) GROUND

- (5) N.C.

- (6) SIGNAL FROM CASSETTE RECORDER TO COMPUTER

- (7) RECORDER 2 MOTOR CONTROL

\*Positions refer to rear panel diagram, above.

(D) PARALLEL I/O SOCKET

25-WAY D TYPE POSITION 7\*

| (1)  | DATA BIT 0 IN      |

|------|--------------------|

| (2)  | DATA BIT 2 IN      |

| (3)  | DATA BIT 4 IN      |

| (4)  | DATA BIT 6 IN      |

| (5)  | DATA BIT 0 OUT     |

| (6)  | DATA BIT 2 OUT     |

| (7)  | DATA BIT 4 OUT     |

| (8)  | DATA BIT 6 OUT     |

| (9)  | +5V                |

| (10) | INPUT STROBE       |

| (11) | HANDSHAKE OUTPUT 1 |

| (12) | HANDSHAKE OUTPUT 2 |

| (13) | HANDSHAKE OUTPUT 3 |

| (14) | DATA BIT 1 IN      |

| (15) | DATA BIT 3 IN      |

| (16) | DATA BIT 5 IN      |

| (17) | DATA BIT 7 IN      |

| (18) | DATA BIT 1 OUT     |

| (19) | DATA BIT 3 OUT     |

| (20) | DATA BIT 5 OUT     |

| (21) | DATA BIT 7 OUT     |

| (22) | GROUND             |

| (23) | GROUND             |

| (24) | INPUT READY        |

| (25) | HANDSHAKE INPUT 1  |

|      |                    |

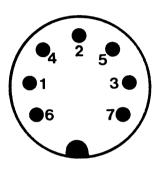

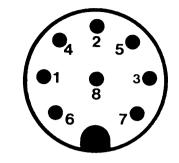

### (E) SERIAL I/O 4

- (1) REQUEST TO SEND

- (2) DATA TERMINAL READY

- (3) TRANSMITTED DATA

- (4) GROUND

- (5) CLEAR TO SEND

- (6) N.C.

- (7) DATA CARRIER DETECT

- (8) RECEIVED DATA

8-PIN DIN SOCKET POSITION 8\*

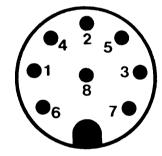

(F) SERIAL I/O 2

# 8-PIN DIN SOCKET POSITION 9\*

- (1) N.C.

- (2) N.C.

- (3) TRANSMITTED DATA

RECEIVED DATA

(4) GROUND(5) CLEAR TO SEND

N.C.

N.C.

(6)

(7)

(8)

PRINTER BUSY LINE

PRINTER BUSY LINE

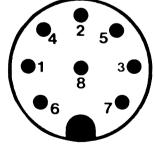

## (G) TTL RGB

### 8-PIN DIN SOCKET POSITION 3

- (1) AUDIO

- (2) MIXED SYNC -

- (3) RED

- (4) GROUND

- (5) BLUE

- (6) GREEN

- (7) LINE SYNC -

- (8) FRAME SYNC -

### CHAPTER 4

### HIGH RESOLUTION GRAPHICS

#### GENERAL INTRODUCTION

The option board for the 480Z gives the machine a high resolution graphics capability. These graphics are of the 'pixel' type. Thus the screen is divided into a regular rectangular array of dots (pixels) each of which can be controlled independently. In this respect the high resolution graphics is similar to the low resolution ('Teletext' style) graphics which are a feature of the basic 480Z. With the high resolution graphics, however, an ordinary text display can be superimposed on the graphics such that, for example, a text character actually overlaps a graphics line. This is not possible with the low resolution graphics where, within a character cell, graphics and text are mutually exclusive. The high resolution graphics display is limited to approximately the top 80% of the screen (actually the top 19.2 character rows). This allows the use of a four line scroller for the text display which will not overlap the graphics area and hence will not interfere with any text in the graphics area, e.g. labels on graph axes.

#### Resolutions

The high resolution graphics can operate in one of three resolutions. These are (in terms of pixels):

| Medium resolution     | 160 | (horizontal) by 96 (vertical)  |

|-----------------------|-----|--------------------------------|

| High resolution       | 320 | (horizontal) by 192 (vertical) |

| Extra high resolution | 640 | (horizontal) by 192 (vertical) |

The simplest of these three modes is the extra high resolution mode in which only one bit of the high resolution graphics screen memory is available to store each pixel on the screen. Thus each pixel can be either on (white) or off (black).

In high resolution mode there are two bits of the memory per pixel. This allows the possibility of four logical intensities (0,1,2,3) for each of the pixels. Each pixel can be set to any of these four intensities independently of any other pixel.

In medium resolution mode there are four bits available per pixel and hence 16 logical intensities are possible and, as with high resolution mode, each pixel may be set independently of the others.

In fact only half of the available graphics memory is required to store a medium resolution 'picture' at four bits per pixel. Thus there is sufficient memory for two such pictures. These two pictures may be displayed and updated independently of each other and, further, a picture

may be updated while the other picture is being displayed. This introduces the possibility of 'drawing' a picture while the other is being displayed and then, when it is complete, swapping the two pictures. Thus the display changes instantaneously even though the picture may have taken considerable amounts of time and computing to generate and draw.

### Look-up Table

In medium and high resolution modes (but NOT extra high resolution mode) the 16 or 4 logical intensities available for each pixel do not correspond directly to the physical intensity displayed on the screen. Instead there is a small (16 byte) look-up table interposed. This has the effect that each of the available logical intensities may be set to any of the available physical intensities. In fact there are 256 intensities available ranging from 0 (black) to 255 (white).

Since the look-up table can be updated very rapidly this introduces the possibility of changing the colours of large areas of the screen simultaneously.

### Colour

The above descriptions have assumed that the graphics output is displayed on a conventional monochrome monitor or television. However the LINK 480Z option board is also capable of driving a colour monitor of the TTL RGB variety. These monitors allow the generation of 8 colours, these being black, blue, red, green, magenta, cyan, yellow and white.

In extra high resolution mode all graphics display (and all text display) will be in black and white only. However medium and high resolution graphics will be displayed in colour. Although there are only 8 physical colours there are still 16 logical colours available in medium resolution and 4 available in high resolution. The colours are still controlled via the look-up table in the same way as for a monochrome display.

### Video Outputs

A 480Z with an option board can be connected to a number of different types of screen. The UHF (phono) socket on the main board can be connected to a standard 625 line television and is tuned to approximately channel 36. Although either black and white or colour televisions will work when connected to this socket, the results, in terms of clarity of picture and readability of textual information, will probably be superior with a black and white set. Only monochrome output is given on the UHF output so that pictures will appear as black and white even on a colour TV set. It is not recommended that a television be used with the 480Z switched into 80character display mode (if the 80-character option is installed) as, although no damage will be done, the display clarity is unlikely to be acceptable. The video (DIN) socket on the main board can be connected to a monochrome video monitor of either the composite video variety (this includes all monitors currently supplied by Research Machines Limited) or the 'wire-frame' variety. All of the video outputs on the main board carry the same information.

The TTL RGB socket on the option board can interface to a TTL RGB colour monitor as described above. Note however that, owing to a certain amount of non-standardisation among the manufacturers of such monitors, it may be necessary to make a minor modification to the computer. However any monitor supplied by Research Machines Limited will work with an un-modified 4802.

The display produced by the colour monitor will not necessarily contain the same information as that displayed by any monitor (or television) plugged into the main board.

The monitor connected to the main board will always show the text (and low resolution graphics) display and will normally display the high resolution graphics superimposed upon this. However it is possible, under software control, to inhibit the display of the high resolution graphics (although it will still be possible to update the high resolution screen while it is disabled so that when re-enabled it will show different information).

Similarly the colour monitor will always show the high resolution graphics but may have the text and low resolution graphics display disabled under software control. Again it is possible to update the text display while it is disabled.

### DETAILED INFORMATION

This section contains information for those who wish to access the 480Z high resolution graphics from assembly language programs.

The 480Z high resolution graphics system is mapped as a group of four I/O ports, HRG ports 0 - 3, which completely control its function. A description of the bit assignments within these ports can be found on page 5.6.

Manipulation of these ports allows the following functions:

- The operating mode of the graphics can be set to be either extra high, high or medium resolution and, in the last case, the page to be displayed can be selected.

- 2) The 16K bytes of screen memory can be accessed both for reading and writing so that pictures can be drawn to the screen, read back from the screen, or modified without having to maintain a copy of the screen contents in user RAM.

- 3) The look-up table which controls the mapping of logical intensities onto physical intensities (or colours) can be written to. It is not, however, possible to read the contents of this RAM and so it is necessary for the user to maintain a copy of its contents.

- 4) It is possible to control the video outputs so that the graphics display on the monochrome monitor may be blanked at will as may the graphics display on the colour monitor.

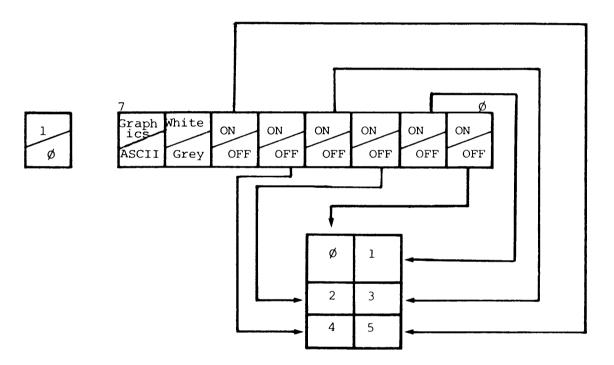

# Selection of Operating Mode

The resolution of the display is controlled by two of the bits in HRG port 2. These two bits are high resolution (L) and extra high resolution (L).

Extra high resolution mode is selected by setting both of these bits to '0'.

High resolution mode is obtained by setting the high resolution bit to '0' and the extra high resolution bit to a '1'.

Medium resolution mode requires that both of these bits be set to 1. In medium resolution it is also necessary to select the page which is to be displayed. This function is performed by the Page number bit in HRG port 2. Setting this bit to a 0 results in the display of page 0 while page 1 is obtained by setting it to a 1. This bit is only relevant in medium resolution.

An invalid operating mode is obtained if the extra high resolution is set to a 0 and the high resolution bit is set to a 1 simultaneously. Although no damage results from selection of this mode it is recommended that it should not be used.

### Accessing the Screen Memory

There are 16K bytes of screen memory of which about 15K bytes are actually used to store the screen information. This memory is arranged as 192 rows of 80 bytes per row. Each of these bytes of memory is then responsible for the generation of 2, 4, or 8 pixels (medium, high and extra high resolutions respectively).

In order to plot a single pixel on the screen at a known position it is first necessary to calculate the X and Y values of the address of the relevant byte, then to decide which bits of that byte to modify, and finally to read the byte, modify it accordingly and restore it to the screen. Each of these steps is described overleaf:

### Calculation of the Byte Address

### The Y Byte Address

In high and extra high resolutions the Y byte address is simply the Y coordinate of the point (in the range 0-191, 0 corresponding to the bottom row of the graphics screen) subtracted from 191.

For medium resolution the Y co-ordinate of the point (in the range 0-95) is doubled and subtracted from 190. The page number which is currently selected for update (0 or 1) is then added to this number.

### The X Byte Address

The X byte address is calculated by dividing the X co-ordinate of the point by 2, 4 or 8 (medium, high or extra high resolutions respectively). The remainder from this division (X remainder) should also be noted as this gives the position of the pixel within the selected byte.

### Mask Generation

In general, the user will want to read a byte, modify it, and write it back to the screen since this allows a single pixel to be modified.

Research Machines' software uses a set of two masks for this purpose. The byte is first 'ANDed' with one mask (the AND mask) and then 'XORed' with the second (the XOR mask). This allows bits within the byte to be unchanged, set, cleared or toggled in any combination. The masks are best chosen using look-up table techniques rather than calculation as this is both quicker and easier.

Suitable masks to allow a point to be plotted at position X rem(ainder) within a byte and of intensity dcba (medium), ba (high) or a (extra high) are given in the table.

| Х   | Medium resolution | High resolution   | Extra resolution      |

|-----|-------------------|-------------------|-----------------------|

| rem | AND mask XOR mask | AND mask XOR mask | AND mask XOR mask     |

| 0   | 11001100 001-001- | 11111100 000000   | 0.1.1.1.1.1. 0.000000 |

| 0   | 11001100 00dc00ba | 11111100 00000ba  | 01111111 a0000000     |

| 1   | 00110011 dc00ba00 | 11110011 0000ba00 | 10111111 0a000000     |

| 2   |                   | 11001111 00ba0000 | 11011111 00a00000     |

| 3   |                   | 00111111 ba000000 | 11101111 000a0000     |

| 4   |                   |                   | 11110111 0000a000     |

| 5   |                   |                   | 11111011 00000a00     |

| 6   |                   |                   | 11111101 000000a0     |

| 7   |                   |                   | 11111110 0000000a     |

### Modifying screen RAM

In order to modify screen RAM it is necessary first to set up the byte address of the byte to be modified. This is done by writing the X byte address to HRG port 1 and Y byte address to HRG port 0. There are no

timing restrictions on these operations.

For general purpose use it is necessary to observe a single timing restriction when accessing screen RAM. This is that the RAM may be accessed ONLY during the line blanking period. The best way to meet this restriction is to wait until the line access bit in HRG port 2 goes active. There will then be sufficient time to read the byte, modify it with the previously calculated masks, and write it back to the screen. Suitable code to perform a complete read-modify-write cycle would be:

| ; On<br>;<br>; | L contains X byte address |                                        |                                                                                          |  |  |

|----------------|---------------------------|----------------------------------------|------------------------------------------------------------------------------------------|--|--|

| ;              | E conta                   | ains XOR mask                          |                                                                                          |  |  |

| ; Se           | t up X and Y a            | addresses                              |                                                                                          |  |  |

|                | LD<br>OUT<br>INC          | C,HRGO<br>(C), H<br>C                  | ; Address of HRG port 0 (Y address)<br>; Set Y address<br>; Now points to X address port |  |  |

|                | OUT                       | (C), L                                 | ; Set X address                                                                          |  |  |

|                |                           | ne access to be i<br>rupts must be dis | nactive (low)<br>abled from here on                                                      |  |  |

|                | DI                        |                                        | ; Disable interrupts                                                                     |  |  |

| LOOP1:         | IN                        | A, (HRG2)                              | ; Status                                                                                 |  |  |

|                | BIT                       | LINACC, A                              | ; Test line access                                                                       |  |  |

|                | JR                        | NZ,LOOP1                               | ; Jump if active                                                                         |  |  |

| ; No           | w wait for lin            | ne access bit to                       | go active (high)                                                                         |  |  |

| LOOP2:         | IN                        | A, (HRG2)                              | ; Status                                                                                 |  |  |

|                | BIT                       | LINACC, A                              | ; Test line access                                                                       |  |  |

|                | JR                        | Z, LOOP2                               | ; Jump if inactive                                                                       |  |  |

| ; No           | w at start of             | line access so d                       | lo Read Modify Write                                                                     |  |  |

|                | IN                        | A, (HRG3)                              | ; Read                                                                                   |  |  |

|                | AND                       | D                                      | ; AND in AND mask                                                                        |  |  |

|                | XOR                       | E                                      | ; XOR in XOR mask                                                                        |  |  |

|                | OUT                       | (HRG3), A                              | ; Write byte back                                                                        |  |  |

| ; Fi           | nished, re-ena            | able interrupts                        |                                                                                          |  |  |

|                | EI                        |                                        |                                                                                          |  |  |

### Accessing the Look-up Table

The look-up table has one byte of memory for each of the available logical intensities. Thus the logical intensity is used as the look-up RAM address

and the corresponding physical intensity is the data byte, 0 corresponding to black and 255 to white.

The look-up table can only be accessed during frame blanking. It is written to by writing the data byte to HRG port 0 and then the 4 bit address to the 4 least-significant bits of HRG port 2. The address is first written with the look-up write bit inactive, then again with it active and finally a third time with it inactive. It is important that after modifying HRG port 2 in this way the port should be restored to its initial value, and a copy should be kept in RAM, before the end of the frame blanking period.

Since it is not possible to read the look-up RAM it is advisable to maintain a copy of its contents in a 16-byte block of RAM. The entire contents of this copy can readily be copied into the look-up RAM during one frame blanking period. Suitable code for such a block update is given below.

; On entry HL points to a 16-byte table.

- ; The first byte of this table should be the value of logical intensity

- ; 0, the second logical intensity 1 etc.

; Note that interrupts should be disabled during this routine

- ; First wait for the start of frame blank

| LOOP1: | IN  | A, (HRG2) | ; | Status               |

|--------|-----|-----------|---|----------------------|

|        | BIT | FBLANK, A | ; | Test frame blank bit |

|        | JR  | NZ, LOOP1 | ; | Jump if active       |

| ; and  | now wait i | or it to become | active (high)        |

|--------|------------|-----------------|----------------------|

| LOOP2: | IN         | A, (HRG2)       | ; Status             |

|        | BIT        | FBLANK, A       | ; Test frame blank   |

|        | JR         | Z, LOOP2        | ; Jump if not active |

; Now in frame access so can output data

|         | LD  | D, 0      | ; D will be logical intensity           |

|---------|-----|-----------|-----------------------------------------|

|         | LD  | в, 16     | ; Count of bytes to output              |

| WRLOOP: | LD  | A, (HL)   | ; Value of physical intensity           |

|         | OUT | (HRGO), A | ; To data port                          |

|         | LD  | A, D      | ; Logical intensity, write bit inactive |

|         | OUT | (HRG2), A | ; to HRG port 2                         |

|         | SET | LWRITE, A | ; Set write bit                         |

|         | OUT | (HRG2), A | ; Output                                |

|         | LD  | A, D      | ; Clear write bit                       |

|         | OUT | (HRG2), A | ; Output it                             |

| INC  | D      | ; Increment logical intensity                    |

|------|--------|--------------------------------------------------|

| INC  | HL     | ; Point to next physical intensity               |

| DJNZ | WRLOOP | ; And write the next byte (unless<br>; finished) |

### ; Finished, re-enable interrupts

ΕI

NOTE: All 16 entries of the colour look-up table should be set up even if less than 16 logical intensities are in use. For example, if high resolution mode is in use, 4 logical intensities are available so the colour look-up table should be loaded with 4 consecutive copies of the 4 logical intensities.

### Controlling the Video Outputs

As mentioned elsewhere there is a feature of the 480Z which allows the high resolution graphics display on the monochrome video outputs from the main board to be suppressed. This is accomplished by setting the HRG inhibit bit in HRG port 2 to a '0'. This does not, however, inhibit in any way the modification of the graphics memory.

Similarly the output of textual information (and low resolution graphics) to the RGB TTL colour monitor socket on the option board may be suppressed by clearing the Video Inhibit bit of HRG port 2. This in no way inhibits the ability to update the VDU screen memory however.

Note that the Video inhibit and HRG inhibit bits are entirely independent of each other and any of the four possible combinations is meaningful.

### Colour Graphics

Most of the above has assumed that a monochrome monitor is being used so that the physical intensities stored in the look-up table are actually the position of the desired colour in a grey scale. If however a colour monitor is being used then only 8 colours are available. There is one bit available to control each of the red, green and blue guns of the monitor. Setting one of these bits causes the appropriate gun to become active. The bits in question are:

| Bit | 4 | BLUE  |

|-----|---|-------|

| Bit | 6 | RED   |

| Bit | 7 | GREEN |

These bits have been chosen so that if the colour graphics are displayed on the monochrome monitor a reasonably sensible looking grey scale is obtained. The colours available are thus:

| Physical<br>Intensity | Colour  |

|-----------------------|---------|

| 0                     | Black   |

| 16                    | Blue    |

| 64                    | Red     |

| 80                    | Magenta |

| 128                   | Green   |

| 144                   | Cyan    |

| 192                   | Yellow  |

| 208                   | White   |

It should be noted that the physical intensities listed above are not the only ones which will produce these colours and that, for the purposes of the colour display, only bits 4, 6 and 7 have any significance and that all others are ignored.

### Opening the Screen

It is possible to open the HRG screen memory for asynchronous access so that the timing restrictions normally imposed on memory accesses are lifted. This is done by clearing the open bit in HRG port 2. However before using this feature the following points should be noted:

- 1) The HRG screen memory is dynamic and must therefore be refreshed at least once every 2ms if its contents are to be retained. When the screen is opened the only refresh which occurs is that due to accessing the memory. In order to maintain refresh it is necessary to access at least the first 64 bytes of two rows whose Y addresses differ in bit 1 every 2ms.

- 2) The screen memory may be corrupted if the open bit is set or reset at any time other than during the line blanking period. Thus before setting or resetting this bit the program should wait for the line access bit in HRG port 2 to become active.

- 3) While the screen is open the HRG display is blanked.

In general it is probably not worthwile using the open bit for purposes other than clearing the screen (as in calls to "RESOLUTION" in BASIC).

### CHAPTER 5

### HARDWARE NOTES

### MEMORY MAPS

The detailed memory map of the LINK 480Z is liable to change between different versions of the firmware. The map given here is for a 64K machine operating under ROS 1.1 (and later versions) and which contains BASIC in ROM and network firmware.

There are 4 available mappings of ROM into the address space, called ROM pages 0 to 3, and controlled by a PROM. The mapping of RAM into the address space is controlled by the firmware.

The usage of the ROM pages is as follows:-

| Page | 0 | : | initialisation, some ROS functions |

|------|---|---|------------------------------------|

| Page | 1 |   | normal operation                   |

| Page | 2 | : | BASIC in ROM                       |

| Page | 3 | : | Not used                           |

# 64K byte system

0C00

0800

0400

0000

(3K)

(2K)

(1K)

(OK)

ROS

| Address      |                | ROM page 0        | ROM page 1   | ROM page 2   | ROM page 3 |

|--------------|----------------|-------------------|--------------|--------------|------------|

|              | (64K)          | -                 |              |              |            |

| FC00         | (63K)          | ROS               | ROS          | ROS          |            |

| F800         | (62K)          | workspace         | workspace    | workspace    |            |

| F400         | (61K)          |                   |              |              |            |

| F000         | (60K)          | ROS               | ROS          | ROS          |            |

| EC00         | (59K)          |                   |              |              |            |

| E800<br>E400 | (58K)<br>(57K) |                   |              |              | +          |

| E000         | (57K)<br>(56K) |                   |              |              | RAM bank 0 |

| DC00         | (50K)<br>(55K) |                   |              |              |            |

| D800         | (54K)          |                   |              |              |            |

| D400         | (53K)          | RAM bank 0        | RAM bank 0   | BASIC ROM    |            |

| D000         | (52K)          |                   |              |              |            |

| CC00         | (51K)          |                   |              |              |            |

| C800         | (50K)          |                   |              |              |            |

| C400         | (49K)          |                   |              |              |            |

| C000         | (48K)          |                   |              | ł            |            |

| BC00         | (47K)          |                   |              |              |            |

| B800         | (46K)          |                   |              |              |            |

| B400         | (45K)          |                   |              |              |            |

| B000         | (44K)          | RAM bank C        | RAM bank C   |              | RAM bank C |

| AC00<br>A800 | (43K)<br>(42K) | RAM Dank C        | RAM Dallk C  |              | KAM Dank C |

| A800         | (42K)<br>(41K) |                   |              | }            |            |

| A000         | (40K)          |                   |              | RAM bank C   |            |

| 9000         | (39K)          |                   |              |              |            |

| 5            | $\sim$         |                   | $\sim$       |              | $\sim$     |

| 8400         | (33K)          | $\sim \sim \circ$ | -            | $\sim$       |            |

| 8000         | (32K)          |                   |              |              |            |

| 7C00         | (31K)          |                   |              |              |            |

| 7800         | (30K)          | RAM bank B        | RAM bank B   | RAM bank B   | RAM bank B |

| 7400         | (29K)          | $\leftarrow$      | ~~~~         |              |            |

|              |                |                   |              |              |            |

| 4000         | (16K)          | ļ                 |              |              |            |

| 3C00         | (15K)          | ROS               | RAM bank A   | RAM bank A   | RAM bank A |

| 3800         | (14K)          |                   | KAPI Dalik A | TAPI DAILY A |            |

| 3400         | (13K)          | RAM bank A        |              |              |            |

| 2000         | (8K)           |                   | $\sim$       | $\sim$       |            |

| 1C00         | (7K)           | BASIC in ROM      |              |              |            |

| 1800         | (6K)           |                   |              |              |            |

| 1400         | (5K)           | _                 |              |              |            |

| 1000         | (4K)           | Network           |              |              |            |

Hardware Notes

### NOTES

If the 64K of RAM consists physically of four rows of 16K RAM chips then:-RAM bank A is RAM bank 4 RAM bank B is RAM bank 8 RAM bank C is RAM bank 12 If, however, there is one row of 64K RAM chips then:-RAM bank A is RAM bank 1 RAM bank B is RAM bank 2 RAM bank C is RAM bank 3 PORTS Port Function Add. 0-17H VDU Port 0 corresponds to the top line of the screen Port 17H corresponds to the bottom line of the screen 18H Control / Status Port 0 19H Control / Status Port 1 1AH Control / Status Port 2 1BH (e) Control / Status Port 3 1DH Control / Status Port 5 (USERIO Port) 20H Main Board CTC Channel 0 - SIO-4 and Cassette Input 2 1H Main Board CTC Channel 1 - Cassette I/O and SIO-2 22н Main Board CTC Channel 2 - Keyboard Interrupts Main Board CTC Channel 3 - 50Hz Interrupts (for repeat key) 23H 24H SIO Channel A (Network) Data Port 25H SIO Channel B (SIO-4) Data Port 26H SIO Channel A (Network) Control / Status Port 27H SIO Channel B (SIO-4) Control / Status Port 28H (b) Maths Chip Data Port 29н Maths Chip Control / Status Port (b) 2AH (b) (Maths Chip Data Port) 2BH (b) (Maths Chip Control / Status Port) Option Board CTC Channel 0 - IEEE Interrupts 2CH (c) 2DH (b) Option Board CTC Channel 1 - Maths Chip Interrupts 2EH (d) Option Board CTC Channel 2 - Real-Time Clock Option Board CTC Channel 3 - Real-Time Clock 2FH (d)

| 30H  | (c) | IEEE 0 Interrupt Status 0    | Interrupt Mask 0                |

|------|-----|------------------------------|---------------------------------|

| 3 1H | (c) | IEEE 1 Interrupt Status 1    | Interrupt Mask 1                |

| 32H  | (c) | IEEE 2 Address Status        |                                 |

| 33H  | (c) | IEEE 3 Bus Status            | Auxiliary Command               |

| 34H  | (c) | IEEE 4                       | Address Register                |

| 35H  | (c) | IEEE 5                       | Serial Poll Register            |

| 36н  | (c) | IEEE 6 Command Pass Thru     | Parallel Poll Register          |

| 37H  | (c) | IEEE 7 Data Input            | Data Output                     |

|      |     |                              |                                 |

| 38H  | (a) | HRGPORT 0 DIL-Switch         | Y Address Look-up Data          |

| 39н  | (a) | HRGPORT 1                    | X Address                       |

| ЗАН  | (a) | HRGPORT 2 HRG Status         | Control Look-up Address         |

| Звн  | (a) | HRGPORT 3 Data Input         | Data Output                     |

|      |     |                              |                                 |

| (a)  |     | Only active if Option Board  | installed                       |

| (b)  |     | Only active if Option Board  | and Maths chip option installed |

| (c)  |     | Only active if Option Board  | and IEEE option installed       |

| (d)  |     | Only active if CTC Option in |                                 |

| (e)  |     | Only active if DAC Option in | stalled                         |

|      |     |                              |                                 |

### Control/Status Ports

Control / Status Port 0 (18H , 24 decimal)

Read = Main Board DIL-Switch

Write = RAM mapping Look-up table

ROS does not maintain a mask for Control Port 0

| Read       |    | Bit |      | Write | 2      |

|------------|----|-----|------|-------|--------|

| DIL-switch | 3  | 7   |      | -     |        |

| DIL-switch | 4  | 6   |      | -     |        |

| DIL-switch | 5  | 5   |      | -     |        |

| DIL-switch | 6  | 4   |      | -     |        |

| DIL-switch | 7  | 3   | Data | bit 3 | (MA17) |

| DIL-switch | 8  | 2   | Data | bit 2 | (MA16) |

| DIL-switch | 9  | 1   | Data | bit 1 | (MA15) |

| DIL-switch | 10 | 0   | Data | bit ( | (MA14) |

|            |    |     |      |       |        |

On writing to port 0 the two least-significant bits of the B register contain the address within the look-up RAM to which the data is written.

Control / Status Port 1 (19H , 25 decimal)

Read = Status Port 1 Write = Control Port 1

ROS maintains a mask for Control Port 1 at OFF01H Read Bit Write Not used 7 Not used Not used 6 Keyboard reset (L) Cassette output bit 5 S'ware USER I/O handshake 3 H'ware USER I/O ready 4 S'ware USER I/O handshake 2 S'ware USER I/O handshake 3 S'ware USER I/O handshake 1 Keyboard ready (L) 2 Single-step enable (H) Frame blank (H) 1 Page bit 1 (ROM mapping) Line blank (L) 0 Page bit 0 (ROM mapping) Control / Status Port 2 (1AH , 26 decimal) Read = Status Port 2 Write = Control Port 2 ROS maintains a mask for Control Port 2 at 0FF02H Read Bit Write JB2 (L = Pressed) 7 80 character mode select (L=40, H=80)JB1 (L = Pressed) Alternate character set 6 (L = normal, H = alternate)JT2 (L = Timed-out) 5 Beep (Connected directly to Loud speaker) JT1 (L = Timed-out)4 Joystick trigger (+ve edge triggered) (trigger joystick timers) SIO-2 received data 3 SIO-2 Transmitted data SIO-2 handshake 2 Cassette motor 2 control (H) Cassette vol. (L=loud) 1 Cassette motor 1 control (H) Cassette input bit Cassette write enable (L) 0 Control / Status Port 3 (1BH , 27 decimal) Read ÷ Keyboard Data Write = D/A Converter (may be connected to the loudspeaker) ROS maintains a mask for Control Port 3 at 0FF03H Control / Status Port 5 (1DH , 29 decimal) Read = USER I/O Input Port Write = USER I/O Output Port ROS maintains a mask for the USER output port at 0FF00H

5.5

Hardware Notes

| HRG Control Ports                                                                                             |                                     |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| These ports are active only if the option board is installed.                                                 |                                     |  |  |  |  |

| HRG Port 0 (38H , 56 decima                                                                                   | 1)                                  |  |  |  |  |

| Read = Option Board DII<br>Write = Y byte Address a                                                           |                                     |  |  |  |  |

| Read                                                                                                          | Bit Write                           |  |  |  |  |

| Option DIL-switch 3                                                                                           | 7 Y Addr. 7 / Look-up Data 7        |  |  |  |  |

| Option DIL-switch 4                                                                                           | 6 Y Addr. 6 / Look-up Data 6        |  |  |  |  |

| Option DIL-switch 5                                                                                           | 5 Y Addr. 5 / Look-up Data 5        |  |  |  |  |

| Option DIL-switch 6                                                                                           | 4 Y Addr. 4 / Look-up Data 4        |  |  |  |  |

| Option DIL-switch 7                                                                                           | 3 Y Addr. 3 / Look-up Data 3        |  |  |  |  |

| Option DIL-switch 8                                                                                           | 2 Y Addr. 2 / Look-up Data 2        |  |  |  |  |

| Option DIL-switch 9                                                                                           | 1   Y Addr. 1 / Look-up Data 1      |  |  |  |  |