# Machine Language Programming Guide

For 380Z and 480Z

Guide to Machine Language Programming for the 380Z and 480Z

Release 1, November 1981

Copyright (c) Research Machines Limited 1981

All rights reserved. Copies—of this publication may be made by customers exclusively for their own use, but otherwise no part of it may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language without the prior written permission of Research Machines Limited, Post Office Box 75, Oxford, England, OX2 OBW. Tel: Oxford (0865) 49791.

The policy of Research Machines Limited is one of continuous development and improvement of its products and services, and the right is therefore reserved to revise this document or to make changes in the computer software it describes without notice. Research Machines Limited make every endeavour to ensure the accuracy of the contents of this document but do not accept liability for any error or omission.

Additional copies of this publication may be ordered from Research Machines Limited at the address above. Please ask for 'Guide to Machine Language Programming for the 380Z and 480Z'.

#### SECOND EDITION

November, 1981

This document is a revision of the 380Z Assembler's Guide written by Colin Opie of the Advisory Unit for Computer Based Education, Hatfield, Hertfordshire, in August 1980.

Research Machines Limited would like to extend their thanks to AUCBE for permission to reprint this manual.

FIRST EDITION 1st Printing 250 August 1980

2nd Printing 250 October 1980

3rd Printing 250 February 1981

SECOND EDITION Reprinted for Research Machines

Limited November 1981

# PREFACE

This is one of a series of texts for users of the Research Machines 380Z microcomputer system. At least three categories of user exist:

- (a) Users who wish to use the microcomputer as a computing aid and who are mainly interested in high level manipulation

- (b) Those who will turn also to low level assembly programming

- (c) Users who would take an interest in the hardware aspects of a microcomputer system

In this text the emphasis lies for those interested in assembly programming.

The Z80 microprocessor is proving itself to many users as a powerful device. It is true that the Z80, like any other microprocessor, will be succeeded at some time, though at present it does represent a "state-of-the-art" in microcomputer technology.

Research Machines Computer Systems 380Z microcomputer uses the power and versatility of the Z80 extremely well. Many people, including industrial and educational establishments are using this particular system. Owing to the number of different configurations available in this system a very general, though comprehensive, approach has been taken for this text. In this way it should make no difference whether the reader is using a 'single Cassette System' or a 'Dual Floppy Disc with Twin-controlled Cassette' system.

A very general introduction to the machine side of the 380Z is first given. This is intended to provide a ground knowledge for the subsequent sections.

The 'Front Panel' of the 380Z is one of its more useful attributes and the first section deals with this. Prior to any machine programming with the 380Z a good working knowledge of this 'panel' is more than useful. It is true that 'Assemblers' take a lot of hard work out of machine-level programming, but this does not mean that assemblers should be a good starting point. The 'front panel' when used properly is an extremely useful tool in the instruction of machine-level programming.

Section 2 deals with the enormous instruction set of the Z80. Similar types of instructions are grouped together to aid explanations. The mechanism of the instruction is given, the effect on flags shown, and so on. In this way it is intended that the text can be a little more than just an 'instruction reference'.

Two appendices exist which include instruction tables, and program examples.

C.N. OPIE 1980

## Acknowledgements:

Much time and effort has been given by various people, notably Peter Andrews, Ken Maynard and Dennis Pitchforth. Unfortunately this edition does not appreciably show their support. Many thanks go to these people and the secretarial staff for all their hard work.

# CONTENTS

# INTRODUCTION

|      | Introduction                                                   | 3<br>4 |

|------|----------------------------------------------------------------|--------|

|      | Bits and Bytes                                                 | 5      |

|      | Hexadecimal                                                    | 5      |

|      | Memory contents and addresses                                  | 5      |

|      | Instructions                                                   | 6      |

|      | Flag register                                                  | 7      |

|      | Programs                                                       | 8      |

|      | Program Layout                                                 | 10     |

|      | Assembly level software                                        | 11     |

|      | How to progress - a suggestion                                 | 12     |

| SECT | ION 1 - FRONT PANEL                                            |        |

|      | Front Panel                                                    | 15     |

| 1.1  | Summary of commands                                            | 16     |

| 1.2  | Display description                                            | 17     |

| 1.3  | Memory pointer commands (M,I,R,U)                              | 18     |

| 1.4  | Reading and Modifying Memory                                   | 20     |

| 1.5  | Modifying Registers                                            | 22     |

| 1.6  | Modifying IO Perts                                             | 23     |

| 1.7  | Utilities (X,P,S,G,N,H,Z,K,J)                                  | 24     |

| 1.8  | Exits (CTRL-B, CTRL-C)                                         | 29     |

| 1.9  | Calling the Front Panel                                        | 30     |

| SECT | ion 2 - z80 instructions                                       |        |

|      | Z80 Instruction set                                            | 33     |

| 2.1  | 8-Bit Loads (LD)                                               | 33     |

| 2.2  |                                                                | 39     |

| 2.3  |                                                                | 41     |

| 2.4  | 8-Bit Arithmetic (ADD, ADC, SUB, SBC, INC, DEC, CPL, NEG, DAA) | 43     |

| 2.5  | 16-Bit Arithmetic (ADD, ADC, SBC, INC, DEC)                    | 49     |

| 2.6  | Jumps (JP)                                                     | 51     |

| 2.7  | Relative Jumps (JR, DJNZ)                                      | 53     |

| 2.8  | Subroutine instructions (CALL, RET)                            | 56     |

| 2.9  | Relative CALLs (CALR)                                          | 58     |

| 2.10 | Restart Calls (RST)                                            | 58     |

| 2.11 | Logical Operations (AND, OR, XOR)                              | 59     |

| 2.12 | Bit Operations (SET, RES, BIT, CCF, SCF)                       | 60     |

| 2.13 | Comparisons (CP)                                               | 61     |

| 2.14     | SRL, RLA, RLCA, RRA, RRCA, RLD, RRD)                                | 62  |

|----------|---------------------------------------------------------------------|-----|

| 2.15     | General Instructions (NOP, HALT, EX, EXX)                           | 64  |

| 2.16     | Input and Output (IN, OUT)                                          | 65  |

| 2.17     | Block Instructions (LDI, LDIR, LDD, LDDR,                           | 03  |

|          | CPI, CPIR, CPD, CPDR, INI, INIR, IND, INDR, OUTI, OTIR, OUTD, OTDR) | 67  |

| 2.18     | Interrupts (DI, EI, RETI, RETN, IMØ, IM1, IM2).                     | 69  |

|          | •                                                                   |     |

|          | APPENDICES                                                          |     |

|          | <del></del>                                                         |     |

| APPENDIX | 1.<br>mmu                                                           |     |

| (Sor     | ruction Tables                                                      | 71  |

| APPENDIX | . 2.                                                                |     |

|          | Programs                                                            | 91  |

| BIBLIOG  | RAPHY                                                               | 99  |

|          |                                                                     | 777 |

#

## INTRODUCTION

To many people low-level programming has the air of confusion and mystery. Bits, bytes, hexadecimal and masking etc. are just terms which increase the complexity. The situation need not be so desperate!

# INTRODUCTION

It is assumed, or at least hoped, that the reader has some knowledge of a high level programming language such as BASIC, FORTRAN, etc. Writing programs at a high level consists of defining a problem and then breaking it down into simple enough steps to be able to program the steps using the computer language. For example to add two numbers and print the result in a high level language we could supply a computer with the following program:

LET FIRST\_NUMBER := 23

LET SECOND\_NUMBER := 47

LET RESULT := FIRST\_NUMBER+SECOND\_NUMBER

PRINT RESULT

STOP

Programming at a low-level is similar but the steps involved need to be much smaller. Instead of working with general names such as 'RESULT' it is necessary to work with 'registers', 'accumulators', and 'memory locations'. It is necessary therefore to know about the architecture of the 'Central Processing Unit' (CPU) or 'Microprocessor Unit' (MPU) so that e.g. register names and properties are known.

In this particular text the emphasis is on how to program the 380Z microcomputer which uses the 'Z80' microprocessor unit. Although the manual aims to enable a user to do this it is advisable to read relevant literature on computer architecture and machine code programming. The main problem with general texts is that it is impossible for them to instruct somebody on how e.g. to put a character onto a screen or out to a printer or in from a keyboard. Normally such routines as character input and output are available through the machine operating system and it is only necessary to know how to set up values for the routine and then how to access the routine. In the case of the 380Z this is done through the 'EMT' instructions and full details of these can be found in the Firmware Reference Manual.

To ease your way in to low-level programming it is suggested that you use the 'front panel' facility of the 380Z. Short programs, or even single instructions can be entered into memory and then executed. In this way you should be able to see literally what the instruction does.

Before a note is made of how instructions look at machine level it would be good to take a brief look at the 'architecture' of the Z80\* microprocessor and a few terms which will appear.

#### THE Z80 CPU

The 380Z uses a member of the 8080 family, the Z80, as its central processor unit (CPU). The Z80 has six general purpose registers in the main register set designated as B, C, D, E, H, and L. There is one accumulator - A, and one flag register - F. This microprocessor unit (MPU) is an 8-bit device and therefore each of the registers occupy an 8-bit byte. Very often the six general purpose registers are used in pairs, i.e. BC, DE and HL, for 16-bit operations. The B register has a special property in as much as it can be used for loop counting. In addition to the above there is an alternate register set designated A', B', C', D', E', F', H', and L' which can be manipulated in exactly the same way as the main register set. There are a set of instruction codes which enable the choice of either the A, F registers or the A', F'

|         | Main Se     | t     | Alternate   | Set        |

|---------|-------------|-------|-------------|------------|

|         | Accumulator | Flags | Accumulator | Flags      |

|         | A           | F     | Α'          | F'         |

| General | В           | C     | В'          | C <b>'</b> |

| Purpose | D           | E     | D'          | E'         |

| l       | Н           | L     | н'          | L'         |

| SPECIAL RE       | GISTERS  |  |  |  |  |  |

|------------------|----------|--|--|--|--|--|

| Program Co       | unter PC |  |  |  |  |  |

| Stack Poir       | nter SP  |  |  |  |  |  |

| Index Regi       | ster IX  |  |  |  |  |  |

| Index Register I |          |  |  |  |  |  |

| Vector           | Memory   |  |  |  |  |  |

| Interrupt        | Refresh  |  |  |  |  |  |

| I                | R        |  |  |  |  |  |

FIG. A) Z8O-CPU Register Set

registers, and a choice of either the B, C, D, E, H, L registers or the B', C', D', E', H', L' registers. This gives a combination of four options on the registers to be used.

Also there are two 8-bit special purpose registers and four 16-bit special purpose registers. In practice the two 8-bit special purpose registers, I and R, are arranged as 8 bits and 7 bits respectively. The I or 'interrupt vector' register is used, as the name implies, when using interrupt levels and is not likely to be used by the beginner. The R or 'refresh' register is not normally used by the programmer but is used by the CPU to refresh 'dynamic' RAM (random-access memory).

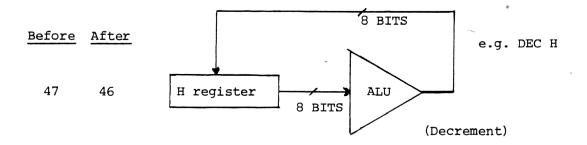

# (i) Program Counter PC

As soon as a byte is fetched from memory the program counter is incremented and so made to point to the next location in store. For a four-byte instruction the program counter will be incremented four times and will therefore automatically point to the next instruction as the current instruction is being executed. Thus the PC register is used as a pointer to the next byte of information to be fetched from memory into the CPU.

## (ii) Stack Pointer SP

The stack is used to store or exchange data and works on the 'last-in-first-out' (LIFO) principal. Data is PUSHED onto the stack and PULLED off the stack under program control. As data is put onto the stack the SP register is decremented and as data is retrieved from the stack the pointer is incremented.

## (iii) Index Registers IX, IY

These are extremely useful special purpose registers which allow the use of 'indexed' addressing within a program. The register is set to a particular location in memory and by the use of particular instructions can act as a pointer to memory within a range of  $-128_{10}$  to +127 bytes from the reference.

#### BITS AND BYTES

As mentioned earlier the Z8O-CPU is an 8-bit device. This means that the CPU will work with 8-bit patterns. The contents of memory locations for example are stored as a pattern of 8 bits, each 'bit' being either a logical 1 or a logical 6. When 8 bits are taken as a unit like this they are commonly called a 'byte'. Another term commonly found in use is the 'word' length. The word length of a CPU is the length in bits of the 'patterns' it usually deals with. So the Z8O-CPU has a word length of 8 bits, which is 1 byte.

To add to the confusion, 1024 bytes of information give lKbytes, (note: not 1000!). The length of a memory is usually measured in kilobytes.

## HEXADECIMAL

As the name suggests, this is base sixteen arithmetic. The numbers from  $\phi$  to fifteen are represented by:

#### Ø 1 2 3 4 5 6 7 8 9 A B C D E F

In binary the number of bits needed to specify 16 variations is 4, in other words a pattern of four bits can be represented by the appropriate HEX value. It follows then that two HEX digits are required to specify an 8-bit pattern, four HEX digits a 16-bit pattern and so on. Where doubt may arise when reading and writing HEX numbers, they should always start with a digit and end with H, e.g.

5H 5CH ØAFH

# MEMORY CONTENTS AND ADDRESSES

It will be noticed that any of the special purpose registers which store pointers to memory (i.e. addresses), e.g. PC register, are 16-bit registers. Suppose that the addresses were only 8 bits long like the memory contents. This means that the highest memory address would be  $\phi$ FFH =  $2^8$  - 1 = 255 (decimal); not very high. To enable the MPU to address an adequate amount of memory, 16-bit addresses are used. This

means that the highest address (without paging techniques) is:

$\emptyset$ FFFFH =  $2^{16} - 1 = 65 535$  (decimal).

This provides then the equivalent of 64Kbytes of memory. Much better.

Digressing a little, if the contents of one memory location was 3EH (i.e. 3E in hex.), it may not be clear whether this is an instruction code or data, and if data what kind of data. For simplicity suppose that if it were data then this would be the ASCII code in hex for the appropriate character. Above it is seen that with 8 bits, 25610 patterns are possible. The ASCII set only requires  $128_{10}$  possibilities, thus this can be accommodated easily. With 8 bits it is also possible to provide 25610 different instruction codes straight off for the CPU. If two-byte instruction codes are implemented the choice is increased by a factor of  $256_{10}$ . If now two address bytes are used on top of the selection code the number of possibilities available far exceeds the range required. For these reasons alone a data word size of 1 byte (8 bits) is perfectly adequate. In practice the instructions occupy from one to four bytes. Owing to the large choice available many of the instructions are in the 'implied' mode. This means that the source and destination of the data is implied by the instruction code, e.g.

| CODE (HEX) | MNEMONIC | DESCRIPTION                                                                                                                                               |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2         | AND D    | Take the 8-bit pattern in the A register and do a bit by bit logical AND with the 8-bit pattern in the D register and put the result into the A register. |

## INSTRUCTIONS

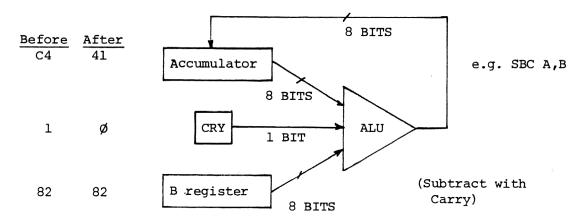

The Z8O microprocessor has 158 different instructions in its repertoire, and an additional two pseudo-instructions are implemented via the 380Z monitor EMTs. Both 8-bit and 16-bit arithmetic is possible. With 8-bit arithmetic, one operand and the result is always in the accumulator. The arithmetic operations available with 8-bits in this category are addition and subtraction only, multiplication and division must be done by software routines. There are, however, two special arithmetic operations which can be used on any register, these being 'increment' and 'decrement'. Boolean operations are also available in this category, these being, AND, OR, EXCLUSIVE-OR, NEGATE, and COMPLEMENT. Note that 'negate' provides the two's complement and 'complement' provides the one's complement - both operations being performed on the accumulator A.

Only limited arithmetic operations are permitted with 16-bits and no boolean operations are available. Unlike adding and subtracting with or without the carry in 8-bit arithmetic, 16-bit arithmetic does not give the option of subtraction without the carry, i.e.

SIZE MNEMONICS

8-bit ADD, ADC, SUB, SBC

16-bit ADD, ADC, SBC

Note that 'increment' and 'decrement' are permitted with 16-bit registers.

Other instructions are concerned with 8-bit loads, 16-bit loads, Jumps -Calls/Returns, and Rotates/Shifts, and other more specialised operations.

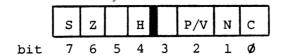

# FLAG REGISTER

As mentioned previously, the Z8O-CPU used in the 380Z system, contains an 8-bit flag register. All the flags available in the CPU can be used when programming or debugging at assembly level with the 380Z. These flags are set in the MPU when most arithmetic and logical operations are performed. They are not usually affected by load instructions except in the more rare instructions such as LD A,R and LDIR. Note that any instruction which does not affect the flags may be interspersed freely between the setting of a flag and inspecting it.

Six of the eight bits in the flag register (F) are used. The 'N' and 'H' flags are used in Binary-Coded-Decimal (BCD) arithmetic and are not likely to be used by the beginner.

#### FIG.B) FLAG REGISTER BIT REPRESENTATION

The remaining flags are:

Sign - set if bit 7 of the result is set (i.e. the number is negative)

Zero - set if the result is zero

P/V - set if the parity of a logical operation is even, or

set if the result of arithmetic causes overflow

Carry - set if the result of arithmetic or logic causes a bit

to flow out of the accumulator

There are only two instructions specifically provided to manipulate the flags:

SCF - set the carry flag

CCF - complement the carry flag

In addition, the following instructions are useful:

AND A - clears the carry flag but does not affect 'A'

XOR A - sets 'A' to zero and clears all but the P/V flag

and the Z flag.

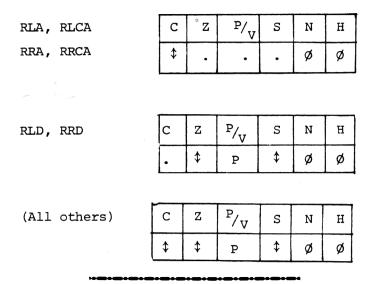

Section 2 of this text covers the instruction set of the Z8O in detail and indicates how, and by what instructions, the flags are affected. The table below gives the 'flag notation' which will be used:

| FLAG NOTATION | MEANING                                                                     |

|---------------|-----------------------------------------------------------------------------|

| •             | Flag not affected                                                           |

| 0             | Flag reset                                                                  |

| 1             | Flag set                                                                    |

| x             | Flag unknown                                                                |

|               | Flag is affected according to the result of the operation $_{\circ}$        |

| IFF           | Content of the interrupt enable flip-flop (IFF) is copied into the P/V flag |

## PROGRAMS

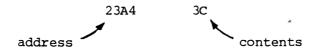

Computers work with patterns of Os and ls The Z8O MPU is an eight bit device and therefore works essentially with patterns 8 bits wide. The program counter collects the contents of memory locations and the MPU operates accordingly on the pattern collected. With this in mind suppose we have the following contents in memory:

The pattern '3C' could be data or it could be an instruction. It is important to realise this when programming at machine level. If the program counter is set in the middle of data (e.g. a series of characters representing a message) and then the Z8O allowed to execute the code then the characters will be interpreted as instructions and anything could happen.

So far the patterns of Os and 1s have been represented by hexadecimal digits, mainly to improve the readability (and save on space when writing the code on paper!). Every instruction to the Z80 MPU has a particular pattern and this could be up to 4 bytes long. This means that the length of a pattern is variable (i.e. 1 to 4 bytes). In the above example the pattern is only one byte long and if it is an instruction then it corresponds to 'take the pattern in the accumulator, treat it as a binary number, and increment that number by 1'. Obviously that last description is a bit long and therefore 'mnemonics' are used to represent the action. In this case it is 'INC A' (INCrement Accumulator). When programming using the 'front panel' it is necessary to enter the hexadecimal representations. When an 'Assembler' is used it is possible to write the program using the mnemonics, which are even easier to read and follow, and the Assembler will work out the necessary machine code.

Just remember that there are two ways of getting the Program into the 380Z:

- i) machine code hexadecimal representation,

- ii) assembler code mnemonic representation.

Much more will be said about the Assembler and assembly code later on but it may be advantageous to have a look at a very short program to see how things are related.

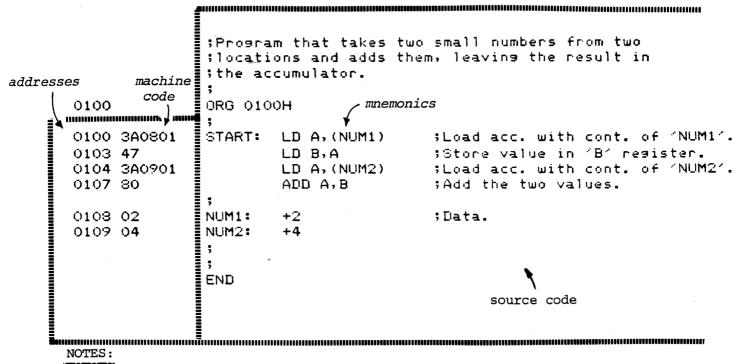

Take a look at the following code:

- i) 'ORG' is merely an instruction to the assembler to say 'start assembling the code at this memory address'. Note that the first address is therefore at  $\emptyset 1 \emptyset \emptyset H$ .

- ii) The 380Z is an eight bit computer and therefore each memory location can only store an eight bit code. The first instruction takes three bytes and therefore uses three locations. Owing to this the second instruction starts in the fourth location from the start. This means that if the program was to be entered using the 'Front Panel' the following would be stored:

| Address       | Contents                                           |

|---------------|----------------------------------------------------|

| Ø1ØØ          | 3A                                                 |

| Ø1Ø1          | <b>ø</b> 8                                         |

| Ø1Ø2          | <b>Ø</b> 1                                         |

| Ø1Ø3          | 47                                                 |

| Ø1Ø4          | -3 <b>A</b>                                        |

| Ø1Ø5          | <b>ø</b> 9                                         |

| Ø1Ø6          | Ø1                                                 |

| Ø1Ø7          | 8Ø                                                 |

| Ø1Ø8          | <b>Ø</b> 2                                         |

| Ø1 <b>Ø</b> 9 | Ø8<br>Ø1<br>47<br>3A<br>Ø9<br>Ø1<br>8Ø<br>Ø2<br>Ø4 |

|               | =                                                  |

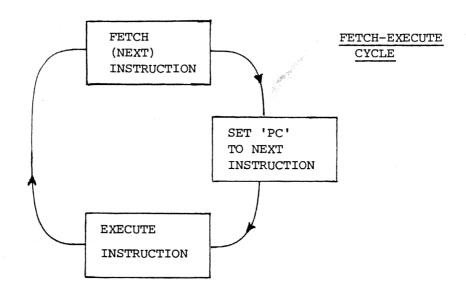

iii) A peculiarity will be seen about the way addresses are stored for instructions. Take 'LD A,(NUM1)' as an example. The instruction has three bytes, one for the instruction itself (3A) and two for the address (NUM1). Now 'NUM1'=location(ØlØ8H) but in the instruction the 'high' byte and the 'low' byte are swapped over. This is always the case with Z8O code and must be carefully adhered to when using the 'Front Panel' to enter programs. When the assembler works out the machine code from the mnemonics the swop is automatically carried out and so mistakes cannot be so easily made. Note also that this means the following is also true:

# LD A, $(12A8H) \Rightarrow 3A A8 12$

- iv) There is no way of stopping this program if it were allowed to run freely. The program could only be run by using the 'single step' facility (see later) of the 'Front Panel' and watching the effects of the instructions.

- v) The 'END' instruction is nothing to do with the program itself but is another directive to the assembler to say that 'this is the end of the code'.

- vi) 'Reading' from a memory location or an MPU register does not destroy the contents of that bit of storage. For example the value of +2 will not disappear from location Ø1Ø8H by putting it into the accumulator. 'Reading' from one location to another is really 'copying'.

## PROGRAM LAYOUT

During the early stages of machine level programming the importance of layout will not appear so relevant because the programs will not be very long. Once the essentials are grasped however the Assembler will start to be used and the programs will become more detailed. When this happens layout is of the utmost importance. There as no hard and fast rules about what should go where but one thing is for sure - absolutely lace the code with comments. An instruction may be placed in the code for one of a number of reasons. For example, 'XOR A' (exclusively-OR accumulator with itself) will unset the carry flag and set the contents of the accumulator to zero, amongst other things. It is important that a comment exists to say what effect is primarily desired from the instruction.

#### ASSEMBLY LEVEL SOFTWARE

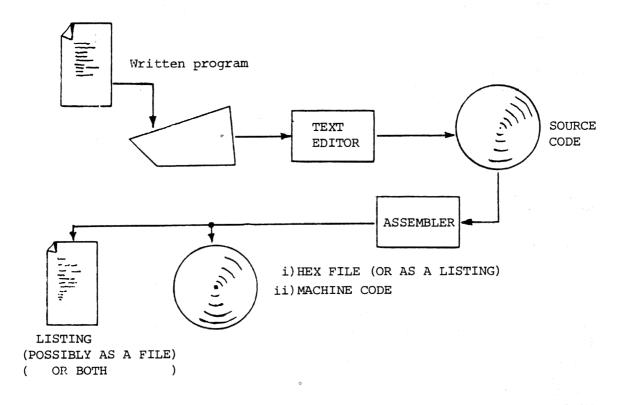

Present documentation by RML on TXED, ZAS/M should be used in conjunction with this manual. It will be helpful to take a closer look at the overall operation of assembler work, and to this end consider again the figure on p.9.

The small block on the left is the machine code and is the form in which the program would be entered using say the front panel. This machine code is produced by the 'Assembler' which uses the 'source code' as its input. The source code is all that which is inside the large block on the right. Once the program or program segment has been written it can be entered into the computer using the RML Text Editor (TXED), and this can then be saved on tape or disc as a source code file. Again this is just the information in the block on the right. The RML Assembler (ZAS/ZASM) can then use this file to produce two new files, a 'Listing file' and a 'Hex file'. A listing file, if printed, would look like the above two blocks joined together. A 'Hex file' is basically just a coded form of the machine code, and can be printed.

So far then we have the following situation:

Obviously the files can be produced on a cassette tape or a disc depending on what kind of system is being used. Note especially that a distinction has been made between the hex file and the machine code. First take a look at the cassette assembler. In this assembler a hex file can be stored or listed and is just a character representation of the machine code. This form is only really useful for producing machine code listings or for sending a copy of the machine code between computers over transmission lines. It is possible as will be seen to get the assembler to produce a machine code file. This is not 'listable', at least not in the sense that the listing would be intelligible. It is the machine runnable form and can be loaded and run in the same way as BASIC or TXED. The

difference is important to realise. The disc version of the assembler (ZASM) is slightly different. In this case it is not possible to get the assembler to produce the machine code file, only the hex file. A utility program called 'LOAD' is then used which takes the hex file as its input and produces a machine code file. Note that with all disc machine-runnable files the 'extension' of this file will be '.COM'.

# HOW TO PROGRESS - A SUGGESTION

Having got this far it should be possible to start looking at the instruction set of the Z80 MPU, keeping in mind the standard Zilog mnemonics for the codes. Chapter 2 deals with the standard Z80 instructions. In order to write useful programs at machine level it will also be necessary to understand the special 380Z monitor routine instructions (e.g. for input/output). Details of these can be found in the Firmware Reference Manual. Before much more is done however it may be wise to first come to grips with using the 380Z Front Panel' facility. This is an essential and powerful tool when programming the 380Z at machine level. Learning even a subset of the features will be a major advantage.

Once familiarity is achieved with the front panel a close look can be made at the programming side. Appendix 2 contains documented examples and these can be used to gradually get to know the instruction set. Not every Z80 instruction is covered but hopefully enough is included to enable the reader to explore the other instructions as and when it becomes necessary. The chapters on the instruction set etc. can be consulted if a more detailed look at the particular instruction types is desired.

As familiarity increases the Assembler will (or should!) start to be used, probably (and advisably) using the Text Editor to produce the source program.

It is hoped that the Appendices will provide quick reference guides to help when writing machine level programs of your own.

#

section 1

# FRONT PANEL

Other than working with the 380Z at a high level, e.g. using BASIC, there are two other modes possible. One is the 'monitor' mode and the other, the 'front panel' mode. When the 380Z is first switched on it is automatically in monitor mode, where the command prompt is a right-arrow (→). This indicates that the user is communicating with the cassette operating system. With discs the bootstrap (B) monitor command can be executed which, provided the 'Operating System' disc is in unit 'A', will load the disc operating system. This will output a short message followed by a new prompt: A>. The 'A' before the arrow indicates the disc unit which will be accessed by default. In either of the above states the front panel mode will be entered on receipt of a 'CTRL-F', and will appear similar to:

| 3A   | F5       | F3       | 18             | E0             | AD             | CD             | С9             | E6AC                 | >PC            |

|------|----------|----------|----------------|----------------|----------------|----------------|----------------|----------------------|----------------|

| 00   | FF       | E4       | 3F             | E6             | AC             | E6             | 9E             | FFBE                 | SP             |

| 00   | EE       | FF       | 00             | 04             | OF             | С3             | 80             | 01D5                 | ΙY             |

| ' 80 | 0F       | 0E       | 01             | FF             | CO             | 6F             | 32             | 7BFA                 | IX             |

| 01   | 00       | F5       | C0             | BA             | F0             | 00             | 18             | EED0                 | HL             |

| : E6 | AC       | F5       | Cl             | BE             | F5             | 00             | 04             | FF04                 | DE             |

| 00   | E4       | 2F       | С3             | 00             | 00             | E6             | AC             | 0000                 | BC             |

|      |          |          | 1              |                | VNC            | Н '            | SZ             | 06FF                 | AF             |

| )    | 00<br>AC | F5<br>F5 | C0<br>C1<br>C3 | BA<br>BE<br>00 | F0<br>F5<br>00 | 00<br>00<br>E6 | 18<br>04<br>AC | EED0<br>FF04<br>0000 | HL<br>DE<br>BC |

#### IO 0000 FF FF FF FF FF FF FF

|      |    |       |     | <b>1</b> |    |      |    |

|------|----|-------|-----|----------|----|------|----|

| E6A0 | C9 | E6A8  | C9  | Ė6B0     | 0C | E6B8 | 0C |

| E6A1 | F7 | E6A9  | CD  | E6B1     | FF | E6B9 | FF |

| E6A2 | 21 | E6AA  | AD  | E6B2     |    | E6BA | Fl |

| E6A3 | FE | E6AB  | ΕO  | E6B3     | 28 | E6BB | FE |

| E6A4 | 06 | >E6AC | 18< | E6B4     | 05 | E6BC | 01 |

| E6A5 | 28 | E6AD  | F3  | E6B5     | 3E | E6BD | C0 |

| E6A6 | 02 | E6AE  | F5  | E6B6     | 17 | E6BE | 3A |

| E6A7 | В7 | E6AF  | 3A  | E6B7     | 32 | E6BF | 0C |

#### FIG 1.1 380Z Front Panel

This 'front panel' is software written and controlled, providing an excellent mechanism for the input and debugging of machine level programs. Commands and delimiters are combined to form capabilities for data input, single stepping, block memory shifts, flag checking, register updating and so on. Useful utilities also exist for pattern searching and hexadecimal calculations.

Note that while in this mode the scroller only operates on the bottom four lines, and that the command prompt is now an exclamation mark (!).

# SUMMARY OF FRONT PANEL COMMANDS

| COMMAND                                                                | ACTION                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Memory Pointer)  M I R U (Memory Pointer Delimi SPACE CARRIAGE RETURN | Remain at present location Increment memory pointer Decrement memory pointer                                                                                                                                                                                                                                                                       |

| LINE FEED                                                              | Move back memory pointer by eight Advance memory pointer by eight                                                                                                                                                                                                                                                                                  |

| (Register Pointer)  < > , ,                                            | Increment Register Pointer Increment I/O Pointer Decrement I/O Pointer Set I/O port to given value                                                                                                                                                                                                                                                 |

| (Utilities)  X P S G N H Z K                                           | Switch Register Display to Alternate set Fill and Test Memory between limits Shift Memory Content Get first occurrence of specified pattern of bytes Find next occurrence of pattern Hexadecimal Calculator Execute single instruction; 'single step'. Continue program execution Set Program Counter to specified address and continue execution. |

| (Exit)<br>CTRL-B<br>CTRL-C                                             | Exit to COS monitor Exit to CP/M                                                                                                                                                                                                                                                                                                                   |

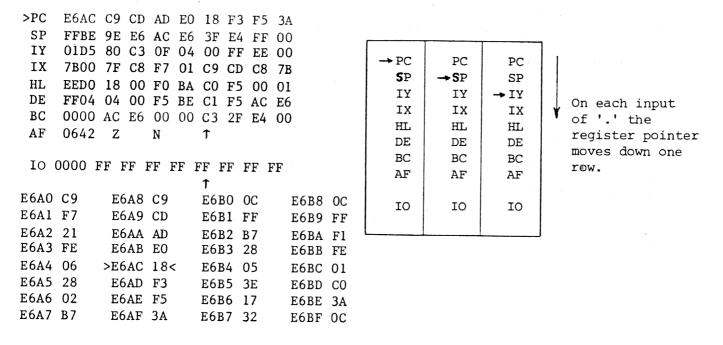

# DISPLAY DESCRIPTION

There are three main areas for the panel, as shown below. At the top is a block of memory relating to the register. In the middle is a line display for the I/O ports, and at the bottom is a block of 32 locations plus associated contents of actual memory.

```

>PC E6AC C9 CD AD E0 18 F3 F5 3A

SP

FFBE 9E E6 AC E6 3F E4 FF 00

IY 01D5 80 C3 OF 04 00 FF EE 00

IX 7BFA 32 6F CO FF 01 0E 0F 80

EEDO 18 00 FO BA CO F5 00 01

HL

FF04 04 00 F5 BE C1 F5 AC E6

0000 AC E6 00 00 C3 2F E4 00

BC

06FF SZ H VNC

IO 0000 FF FF FF FF FF FF FF

1

E6A0 C9

E6A8 C9

E6B0 0C

E6B8 0C

E6A1 F7

E6A9 CD

E6B1 FF

E6B9 FF '

E6A2 21

E6B2 B7

E6AA AD

E6BA F1

E6A3 FE

E6AB E0

E6B3 28

E6BB FE

E6A4 06

>E6AC 18<

E6B4 05

E6BC 01

E6A5 28

E6AD F3

E6B5 3E

E6BD C0

E6A6 02

E6AE F5

E6BE 3A

E6B6 17

E6A7 B7

E6AF 3A

E6B7 32

E6BF OC

```

FIG 1.2 - 380Z Front Panel

Consider first the top region, the register display area. The registers are denoted by their standard Zilog mnemonics: PC, SP, IY, IX, HL, DE, BC and AF; referring to the Program Counter, Stack Pointer, two Index Registers, three 16-bit registers, Accumulator and Flag Register. Immediately to the right of these mnemonics are four-digit hexadecimal numbers. These numbers display the contents of the registers. To the right again, of all but the A and F registers, is a row of eight two-digit hexadecimal numbers. These numbers represent the memory contents as addressed by the contents of the registers. The register pointer, at the foot of the fourth column from the left, points to the actual memory contents as addressed by the register. To the left of this byte are four bytes of memory directly below the register content, and to the right are three bytes of memory directly above the register content.

In the case of the 'AF' row this would not be very meaningful and so the content of the flag register is displayed using the letters: S, Z, H, V, N, and C to indicate the presence of any of these flags. For example, the presence of the C means that the Carry flag has been set. Note that these letters are the standard symbols used by Zilog, with the letter V acting for the Zilog P/V symbol.

Consider now the middle region, the I/O port display area. This line display is associated with the upper register region in as much as the register pointer to the left of the mnemonics, initially pointing

to the Program Counter, can be made to point to this row.

The lower part of the display, the memory location display, is completely separate from the above two regions. It consists of a block of 32 memory location addresses together with their associated contents. Approximately half way down the second block of eight are the memory pointers. When modifying or inserting memory content it is at the location pointed to by these pointers that the memory content can be changed.

# MEMORY POINTER COMMANDS (M, I, R, U)

These four commands provide a mechanism for aligning the memory pointer on the front panel to specific locations.

# 1.3.1 M

Format: e.g.  $\underline{M} > \underline{21C4}$

Typing M as a command to the front panel prompt (!) will result in the command being echoed plus a prompt (>) for a hexadecimal value. This value should be a four-digit address. If less than four digits are entered then leading zeroes will be assumed:

If more than four digits are entered then the digits displayed will be shifted to the left displaying the last four digits entered, this being the address used for the move. (On some machines you may have to DELETE).

On entering the address and pressing the RETURN key the memory location display will adjust itself so that the memory pointer is aligned with the location specified.

| >PC       0203       00       C3       09       02       CD       E9       03       C3         SP       FFBE       9E       E6       AC       E6       3F       E4       FF       00         IY       01D5       80       C3       0F       04       00       FF       EE       00         IX       7B00       7F       C8       F7       01       C9       CD       C8       7B         HL       EED0       18       00       F0       BA       C0       F5       00       01         DE       FF04       04       00       F5       BE       C1       F5       A2       13         BC       0000       03       02       00       00       C3       2F       E4       00         AF       0642       Z       N       T       T       T       T | >PC 0203 00 C3 09 02 CD E9 03 C3 SP FFBE 9E E6 AC E6 3F E4 FF 00 IY 01D5 80 C3 0F 04 00 FF EE 00 IX 7800 7F C8 F7 01 C9 CD C8 7B HL EED0 18 00 F0 BA C0 F5 00 01 DE FF04 04 00 F5 BE C1 F5 AC E6 BC 0000 03 02 00 00 C3 2F E4 00 AF 0642 Z N                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO 0000 FF FF FF FF FF FF FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IO 0000 FF FF FF FF FF FF FF FF                                                                                                                                                                                                                                   |

| 1396 F5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | E6A0 C9 E6A8 C9 E6B0 OC E6B8 OC E6A1 F7 E6A9 CD E6B1 FF E6B9 FF E6A2 21 E6AA AD E6B2 B7 E6BA F1 E6A3 FE E6AB E0 E6B3 28 E6BB FE E6A4 O6 >E6AC 18< E6B4 O5 E6BC O1 E6A5 28 E6AD F3 E6B5 3E E6BD CO E6A6 O2 E6AE F5 E6B6 17 E6BE 3A E6A7 B7 E6AF 3A E6B7 32 E6BF OC |

FIG. 1.3 - EFFECT of 'M' COMMAND

The example above (Fig. 1.3) shows the effect of the command:  $M \geq \text{E6AC}$ , on the original display.

## 1.3.2 I

Format: ! I

This command sets the memory pointer to the address as specified by the memory contents presently pointed to. Note that it is only necessary to enter the command in response to the prompt (!), NO RETURN is required.

Suppose the memory display around the pointer is as follows:

EØ4A F5 EØ4B CD → EØ4C 56 ← EØ4D EØ EØ4E D5

On the 'I' command the byte pointed to by the memory pointer and the following byte (56,EØ) will be taken as the absolute address to move to, in standard machine format which is LSB first followed by MSB; which in this case would give an address of EØ56. The memory display around the pointer would then become:

EØ54 E3 EØ55 C9 → EØ56 D5 ← EØ57 21 EØ58 Ø8

#### 1.3.3 R

Format: ! R

This command is similar in operation to the 'I' command and sets the memory pointer to the relative address as specified by the memory contents presently pointed to. The result of the relative move will be exactly the same as that under normal program execution. In view of this the 'R' command is an extremely useful tool for testing relative calls and jumps in user programs.

Suppose the memory contents around the pointer are as follows:

E69A 28 →E69B FC← E69C EF

On the 'R' command the byte pointed to by the memory pointer will be taken as the relative position of the location to move to. The code FC is interpreted as -4 (decimal) and therefore the memory contents around the pointer will now be:

E697 C9 → E698 F7 ← E699 1D E69A 28

Note that the pointer has apparently only skipped backwards three locations and not the four which were specified. This is because under normal program execution when an instruction is fetched, the program counter (PC) is automatically advanced to the first byte of the next instruction. On executing a relative jump this has to be taken into account.

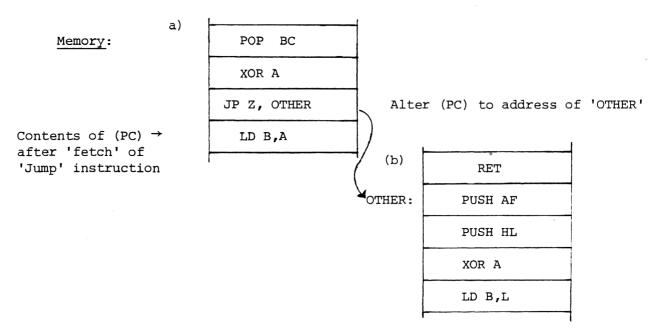

# 1.3.4 U

Format: !U

This is another command (like I and R) which sets the memory pointer by reference to an already existing location, this time the Program Counter. The figure below (Fig.1.4) shows the effect of the 'U' command. In the initial state the memory pointer is aligned to some particular location in memory, and the program counter (PC) is pointing to location E6AC. On execution of the 'U' command the memory display is updated so that the memory pointer now aligns itself with the address given by the program counter.

| >PC          | E6AC     | C9 CD         | AD       | E0 1 | 8 F3       | F5       | 3A           |          | Ē | >PC                  | E6AC | C9        | CD       | AD   | EO   | 18   | F3           | F5       | 3A |                      |     |

|--------------|----------|---------------|----------|------|------------|----------|--------------|----------|---|----------------------|------|-----------|----------|------|------|------|--------------|----------|----|----------------------|-----|

| SP           | FFBE     | 9E E6         | AC       | E6 3 | 3F E4      | FF       | 00           |          |   | SP                   | FFBE | 9E        | E6       | AC   | E6   | 3F   | E4           | FF       | 00 |                      |     |

| IY           | 01D5     | 80 C3         | 0F       | 04 0 | 00 FF      | EE       | 00           |          | Ī | IY                   | 01D5 | 80        | С3       | 0F   | 04   | 00   | FF           | EE       | 00 |                      |     |

| IX           | 7B00     | 7F C8         | F7       | 01 C | :9 CD      | C8       | 7B           |          |   | IX                   | 7B00 | 7F        | С8       | F7   | 01   | C9   | CD           | C8       | 7B |                      |     |

| $^{\rm HL}$  | EED0     | 18 00         | F0       | BA C | 0 F5       | 00       | 01           |          | Ē | $^{\rm HL}$          | EED0 | 18        | 00       | F0   | BA   | C0   | F5           | 00       | 01 |                      |     |

| DE           |          | 04 00         |          |      |            |          |              |          | Ī | DE                   | FF04 | 04        | 00       | F5   | BE   | Cl   | F5           | AC       | E6 |                      |     |

| BC           | 0000     | AC E6         | 00       | 00 C | 3 2F       | E4       | 00           |          | Ī | BC                   | 0000 | AC        | E6       | 00   | 00   | C3   | 2F           | E4       | 00 |                      |     |

| AF           | 0642     | Z             | N        | T    | •          |          |              |          | Ē | AF                   | 0642 | Z         |          | N    |      | Ť    |              |          |    |                      |     |

|              |          |               |          |      |            |          |              |          | Ī |                      |      |           |          |      |      |      |              |          |    |                      |     |

| IO           | 0000     | FF FF         | FF F     | F FF | FF         | FF I     | FF           |          | Ē | 10                   | 0000 | FF F      | F I      | FF 1 | FF 1 | FF I | F I          | FF 1     | FF |                      |     |

|              |          |               |          | 1    |            |          |              |          | Ī |                      |      |           |          |      |      | T    |              |          |    |                      |     |

| 2029         |          | 2031          |          |      | 039        |          | 2041         | 55       | Ī | E6A0                 | C9   | E6        | A8       | C9   |      | E61  | 30 (         | OC       |    | E6B8                 | OC. |

| 202A         |          | 2032          |          |      | 03A        |          | 2042         |          | Ī | E6A1                 | F7   |           |          | CD   |      | E6E  |              |          |    | E6B9                 | FF  |

| 202B         |          | 2033          |          |      | :03B       |          | 2043         | D2       | Ē | E6A2                 | 21   | E6        | AA       | AD   | ٠    | E6E  | 32 I         | 37       |    | E6BA                 | Fl  |

| 202C         | AD       | 2034          | D2       | 2    | :03C       | 4 E      | 2044         | 46       | Ē | E6A3                 | FE   | E6        | AB       | ΕO   |      | E6E  | 3 2          | 28       |    | E6BB                 | FE  |

|              |          |               |          |      |            |          |              |          |   |                      |      |           |          |      |      |      |              |          |    |                      |     |

| 202D         | AA       | >2035         | BE<      | 2    | 03D        | D4       | 2045         | 52       | Ē | E6A4                 | 06   |           |          |      | <    |      |              |          |    | E6BC                 | 01  |

| 202D<br>202E |          | >2035<br>2036 |          |      | 03D<br>03E |          | 2045<br>2046 |          |   | E6A4<br>E6A5         |      | >E6       | AC       | 18   | <    | E6E  | 34 (         | )5       |    | E6BC<br>E6BD         |     |

|              | AF<br>DE |               | BD<br>BC | 2    |            | 41<br>42 |              | C5<br>49 |   | E6A4<br>E6A5<br>E6A6 | 28   | >E6<br>E6 | AC<br>AD |      | <    |      | 34 (<br>35 ( | )5<br>3E |    | E6BC<br>E6BD<br>E6BE | C0  |

FIG. 1.4 - EFFECT OF 'U' COMMAND

When 'single stepping' through machine level programs this command is extremely useful in that it updates the memory display quickly, to correspond with the program counter movements.

# 1.4 Reading and Modifying Memory

SPACE

CARRIAGE RETURN

- (minus)

/ (backslash)

LINE FEED

and used to read and modify local blocks of memory. To read memory, i.e. look at the contents given by the display, the delimiters are used on their own. To modify memory locations the delimiters are used in conjunction with a two-digit hexadecimal value, which is to be the new contents of the memory location pointed to by the memory pointer.

## 1.4.1 Reading

When purely examining the contents of local memory the delimiters are used on their own in response to the prompt (!). They are not echoed back in any way although the four-line scroller will scroll up at the bottom of the display. Used in this mode they have the following effects:

SPACE = Remain at present location. Do nothing.

CARRIAGE RETURN = Increment the memory pointer. If initially at address ED73; will now point to ED74.

Decrement the memory pointer. If initially at address EC5A; will now point to EC59.

LINE FEED = Advance the memory pointer by eight locations. If initially at address EC2Ø; will now point to EC28.

## 1.4.2 Modifying

When modifying memory locations the above delimiters are used together with a two-digit hexadecimal value. If only one digit is entered as the value then a leading zero is assumed:

If more than two digits are entered then the last two digits entered will be taken as the value.

Format: e.g. ! 3B < delimiter >

To modify the memory content of the location pointed to by the memory point the hexadecimal value must be entered followed by any one of the delimiters, in response to the prompt (!). The value specified will be entered into the location originally pointed to and then the memory pointer will be adjusted as defined by the delimiter.

For example, suppose that the command: 4F < carriage return > had been input with the initial memory display around the memory pointer being:

21A3 CD 21A4 34 → 21A5 ØØ ← 21A6 ØØ

The initial location pointed to (21A5) would have a new content (4F) entered and then the memory pointer would be modified accordingly; in this case incremented by one location. The memory display around the pointer would therefore become:

21A4 34 21A5 4F → 21A6 ØØ ← 21A7 ØØ

Note that if an attempt is made to modify the contents of ROM (Read-Only-Memory) then although the command will be accepted and the effect of the delimiter exercised, the memory modification will be nullified.

# 1.5 Modifying Registers

First of all, another look at the front panel. In the upper region of the display, the Register display, to the left of the register mnemonic for the Program Counter (PC) there is a pointer. By using the register pointer delimiter '.' (full stop), this pointer can be moved down to point to any of the register mnemonics (including the IO display).

(a) 380Z Front Panel

(b) Successive effects of '.' command

FIG 1.5 FRONT PANEL AND EFFECT OF '.' COMMAND

On reaching the IO display, another '.' input will set the register pointer back to the program counter (PC).

The purpose in being able to move the register pointer around in this way is that it is the register pointed to which can be modified. To modify the register pointed to a four-digit hexadecimal value is expected plus the '.' delimiter.

Format: e.g. !Ø2Ø3 <.>

Normal hexadecimal input rules apply here, meaning that leading zeroes are assumed if necessary and the last four digits will be accepted if more than four are entered.

A point to watch out for here is that if the wrong delimiter is used, e.g. < carriage return >, then it will be a memory location which will be altered - not the register. It will be noticed that the use of the register pointer delimiter in this mode does not result in the register pointer being moved. Hence the delimiter has two roles.

- (a) When used alone it specifies a shift of the register pointer;

- (b) When used together with a hexadecimal value it specifies a modification to the appropriate register.

As soon as the delimiter is entered the hexadecimal value given will be entered into the register pointed to. Note that the contents of the eight-byte row displayed to the right of the register content display also changes to coincide with the memory locations denoted by the new content of the register. In the case of the AF register note that e.g. POFF will place 'FF' into the flag register and hence display all the flags available.

## 1.6 Modifying IO Ports

The Input/Output ports are addressed using the delimiters given in the summary at the beginning of this chapter. The 'contents' display of the ports will not alter however unless particular ports are explicitly addressed. It is unusual for the beginner to use these ports and they are normally only used when dealing with control applications.

# 1.7 Utilities (X, P, S, G, N, H, Z, K, J)

Nine routines exist within the 'front panel' of the 380Z and are designed specifically to ease the formation and debugging of machine level programs.

# 1.7.1 X

Format: ! X

This command will enable the alternate set of registers, available within the Z8O microprocessor, to be displayed in place of the original set.

# IO 0000 FF FF FF FF FF FF FF

|      |    |       |     | Τ    |    | *      |     |

|------|----|-------|-----|------|----|--------|-----|

| 1497 | D6 | 149F  | 21  | 14A7 | FE | 14AF   | CD  |

| 1498 | 03 | 14A0  | 00  | 14A8 | 1A | 14BO   | А3  |

| 1499 | F1 | 14A1  | 01  | 14A9 | 37 | 14B1   | 14  |

| 149A | C3 | 14A2  | C9  | 14AA | C8 | 14B2   | D0  |

| 149B | 69 | >14A3 | CD< | 14AB | В7 | 14B3   | FE  |

| 149C | 05 | 14A4  | E5  | 14AC | 28 | 14B4   | OA. |

| 149D | 36 | 14A5  | 26  | 14AD | F5 | 14B5   | 28  |

| 149E | 00 | 14A6  | D8  | 14AE | C9 | _ 14B6 | 04  |

|      |    |       |     |      |    |        |     |

#### FIG. 1.6 - ALTERNATE REGISTER SET

Each successive 'X' command input to the prompt (!) will exchange the set of registers displayed. Note that when the alternate set is being displayed each of them (HL', DE', BC', AF') is flagged with an apostrophe. The set of registers displayed by the front panel is the set which will be used in the running of a program, so it is important before running programs from the front panel that the correct set is available.

#### 1.7.2 P

Format: e.g.

$$\frac{!P}{FIRST} > \underline{\emptyset2\emptyset\emptyset}$$

$LAST > \underline{\emptyset2\emptyset9}$

$WITH > \overline{AF}$

Two functions are carried out when the command 'P' is entered in response to the command prompt (!). A section of memory is 'filled' and then 'tested'. On entry of the command the routine prompts for the first and last addresses to be filled. It then prompts for the two-digit hexadecimal value which is to be entered into the locations. An ?ERR? message will be output and a return made to the Cassette Operating System (prompt  $\rightarrow$  ), if the final address is less than the first address.

On entering the 'fill with' byte, all locations between the specified limits, inclusive, will be filled with this byte. This command has no effect on the memory pointer whatsoever.

As the memory is being filled, it is also read back to check that the specified change has taken place. If an error is detected then the ?ERR? message is output and the front panel re-entered with the memory pointer aligned to the location causing the error. To continue the fill and test routine at the next byte the 'K' command can be entered, or an exit to either of the operating systems made (CTRL-B,CTRL-C). This facility does provide a very convenient mechanism for testing memory integrity, memory type (RAM/ROM), or end of user memory. Note that non-existent memory reads as FF(hex.).

| >PC E6AC C9 CD AD E0 18 F3 F5 3A                                                                                                                                                                                                                                                                                                                                                                                                                                                               | >PC E6AC C9 CD AD E0 18 F3 F5 3A                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP FFBE 9E E6 AC E6 3F E4 FF 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SP FFBE 9E E6 AC E6 3F E4 FF 00                                                                                                                                                                                                   |

| IY 01D5 80 C3 OF 04 00 FF EE 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                | >PC E6AC C9 CD AD E0 18 F3 F5 3A  SP FFBE 9E E6 AC E6 3F E4 FF 00  IY 01D5 80 C3 0F 04 00 FF EE 00  IX 7B00 7F C8 F7 01 C9 CD C8 7B  HL EED0 18 00 F0 BA C0 F5 00 01  DE FF04 04 00 F5 BE C1 F5 00 02                             |

| IX 7B00 7F C8 F7 01 C9 CD C8 7B                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IX 7B00 7F C8 F7 01 C9 CD C8 7B                                                                                                                                                                                                   |

| HL 2A30 00 00 20 85 00 58 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HL EEDO 18 00 FO BA CO F5 00 01                                                                                                                                                                                                   |

| DE 0000 AC E6 00 00 C3 2F E4 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DE FF04 04 00 F5 BE C1 F5 00 02                                                                                                                                                                                                   |

| BC 8518 FF FF FF FF FF FF FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BC 0000 AC E6 00 00 C3 2F E4 00                                                                                                                                                                                                   |

| AF OC95 S H V C T                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AF 0642 Z N T                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                   |

| IO 0000 FF FF FF FF FF FF FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TO 0000 PR PR PR PR PR PR PR                                                                                                                                                                                                      |

| 10 0000 11 11 11 11 11 11 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IO 0000 FF FF FF FF FF FF FF                                                                                                                                                                                                      |

| ↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10 0000 FF FF FF FF FF FF                                                                                                                                                                                                         |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>†</b>                                                                                                                                                                                                                          |

| <b>↑</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 01F4 00 01FC 00 0204 AF 020C C3                                                                                                                                                                                                   |

| 01F4 00 01FC 00 0204 E9 020C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01F4 00 01FC 00 0204 AF 020C C3 01F5 00 01FD 00 0205 AF 020D 00                                                                                                                                                                   |

| 1F4 00 01FC 00 0204 E9 020C C<br>01F5 00 01FD 00 0205 03 020D 0                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 01F4 00 01FC 00 0204 AF 020C C3 01F5 00 01FD 00 0205 AF 020D 00 01F6 00 0206 AF 020E 04                                                                                                                                         |

| 01F4 00 01FC 00 0204 E9 020C C<br>01F5 00 01FD 00 0205 03 020D 0<br>01F6 00 01FE 00 0206 C3 020E 0<br>01F7 00 01FF 00 0207 03 020F F                                                                                                                                                                                                                                                                                                                                                           | 1 01F4 00 01FC 00 0204 AF 020C C3 01F5 00 01FD 00 0205 AF 020D 00 01F6 00 01FE 00 0206 AF 020E 04 01F7 00 01FF 00 0207 AF 020F F7                                                                                                 |

| 01F4     00     01FC     00     0204     E9     020C     C       01F5     00     01FD     00     0205     03     020D     0       01F6     00     01FE     00     0206     C3     020E     0       01F7     00     01FF     00     0207     03     020F     F                                                                                                                                                                                                                                  | 01F4 00 01FC 00 0204 AF 020C C3 01F5 00 01FD 00 0205 AF 020D 00 01F6 00 01FE 00 0206 AF 020E 04 01F7 00 01FF 00 0207 AF 020F F7 01F8 00 >0200 AF< 0208 AF 0210 22                                                                 |

| 1F4 00 01FC 00 0204 E9 020C C<br>01F5 00 01FD 00 0205 03 020D 00<br>01F6 00 01FE 00 0206 C3 020E 00<br>01F7 00 01FF 00 0207 03 020F F<br>01F8 00 >0200 C3< 0208 04 0210 2                                                                                                                                                                                                                                                                                                                      | 01F4 00 01FC 00 0204 AF 020C C3 01F5 00 01FD 00 0205 AF 020D 00 01F6 00 01FE 00 0206 AF 020E 04 01F7 00 01FF 00 0207 AF 020F F7 01F8 00 >0200 AF< 0208 AF 0210 22 01F9 00 0201 AF 0209 AF 0211 FE                                 |

| 01F4       00       01FC       00       0204       E9       020C       C         01F5       00       01FD       00       0205       03       020D       0         01F6       00       01FE       00       0206       C3       020E       0         01F7       00       01FF       00       0207       03       020F       F         01F8       00       >0200       C3       0208       04       0210       2         01F9       00       0201       09       0209       CD       0211       F | 01F4 00 01FC 00 0204 AF 020C C3 01F5 00 01FD 00 0205 AF 020D 00 01F6 00 01FE 00 0206 AF 020E 04 01F7 00 01FF 00 0207 AF 020F F7 01F8 00 >0200 AF< 0208 AF 0210 22 01F9 00 0201 AF 0209 AF 0211 FE 01FA 00 0202 AF 020A E9 0212 03 |

a) Initial state

(b) After format example (above) entered

FIG 1.7 - EFFECT OF 'P' COMMAND (e.g.)

#### 1.7.3 S

Format: e.g.  $\frac{! S}{FIRST} = \frac{0200}{0203}$  TO = 0208

A block of memory, as defined by the user in response to the FIRST and LAST prompts, is shifted to another area of memory store as defined by the user in response to the TO prompt.

The shift routine is entered by typing 'S' in response to the command prompt(!), and three four-digit hexadecimal addresses are required for operation. All contents of the locations specified by the user, inclusive, are moved sequentially to another area of memory starting at the address specified. The memory pointer is not affected by this command. It is possible to shift a block up or down the memory and the source area and the destination area are allowed to overlap. If however the final address is less than the first address specified, an ?ERR? message will be output and a return made to the Cassette Operating System(prompt -).

Note that the memory contents are not tested, as in the 'P' command, and therefore any attempt to overwrite ROM (Read Only Memory), or access non-existant memory, will be nullified- though not pointed out to the user.

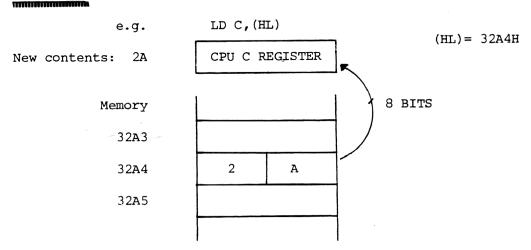

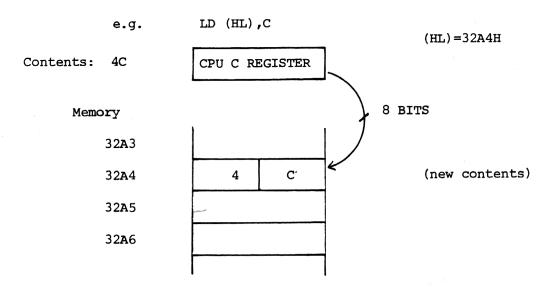

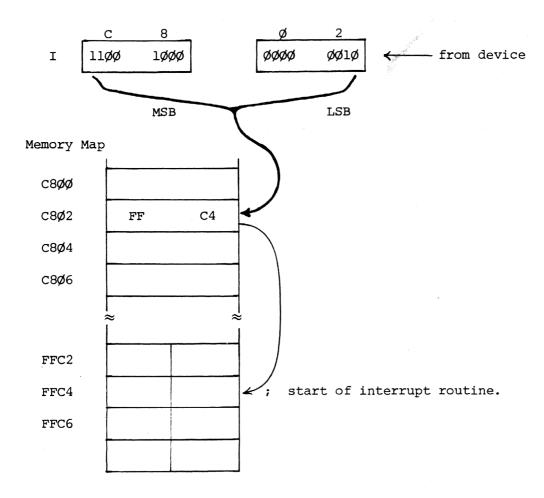

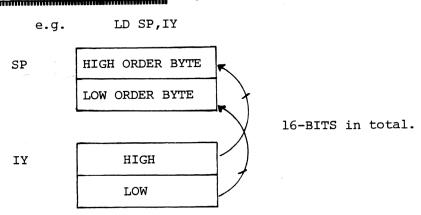

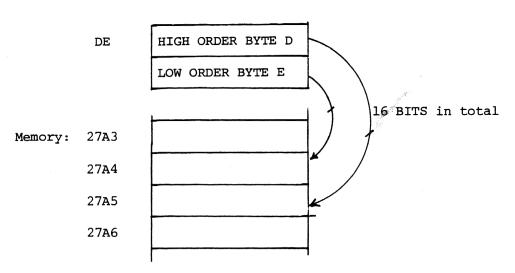

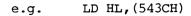

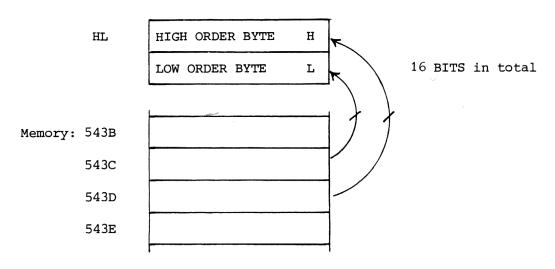

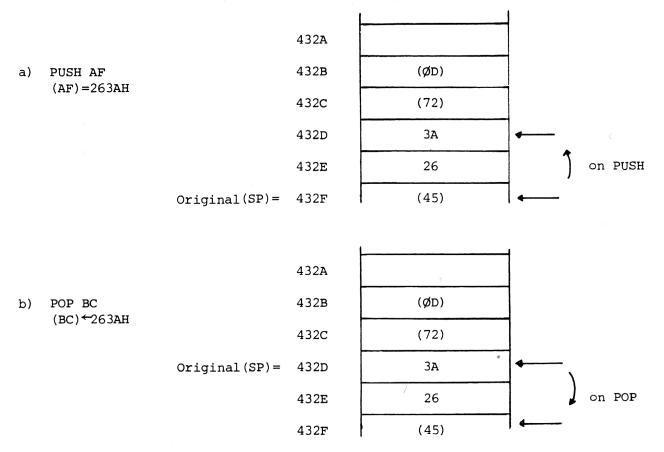

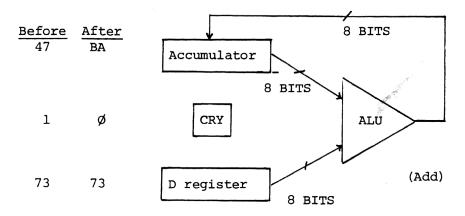

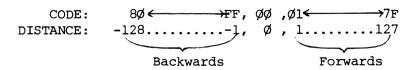

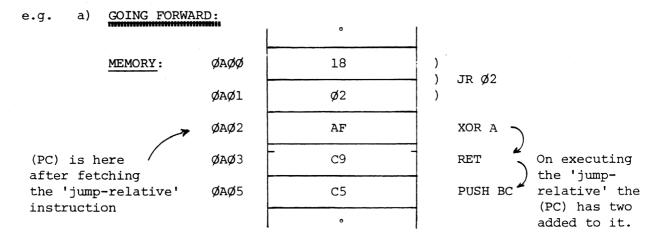

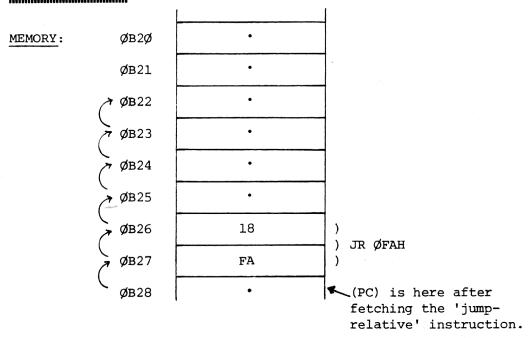

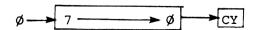

| >PC E6AC C9 CD AD E0 18 F3 F5 34       | ⇒ >PC E6AC C9 CD AD E0 18 F3 F5 3A               |