This section describes the contents of the technical description chapter and provides a technical overview of the terminal.

This technical description is intended to provide an understanding of the terminal operating principles for Field Service, depot repair, and engineering personnel. The description considers the terminal to be several functional or replaceable subunits. Each subunit is described in its own section. Several subunits interact. Those interactions are discussed in the section about the subunit most involved in the particular process. For example, power-up involves the nonvolatile RAM but is described in the microprocessor section. Scrolling has its own section because it is a complex process that involves the microprocessor and video processor equally.

Each section describes the hardware first and the associated firmware operations second. This section contains a block diagram level discussion of the terminal hardware and firmware. More detail is provided in the functional block descriptions in later sections. Refer to the VT100 series Field Maintenance Print Set, No. MP00633, for circuit details while studying this manual.

Many terms are written out the first time they appear, with an abbreviation or mnemonic in parentheses after it. The abbreviation is generally used after that. There is a glossary of abbreviations and signal names in the appendices of this manual. Numbers may be given in binary, octal, decimal, or hexadecimal (hex). The normal form will be decimal for scalar or ordinal values, and hex for data and addresses. Numbers are subscripted B for binary, Q for octal, H for hex, and no subscript for decimal.

The VT100 is a complete computer input and output terminal that has a keyboard like a typewriter and displays its data on a video screen. It fits into two compact packages; the keyboard is flexibly attached to the main cabinet by a coiled cable. Refer to Figure 4-1-1.

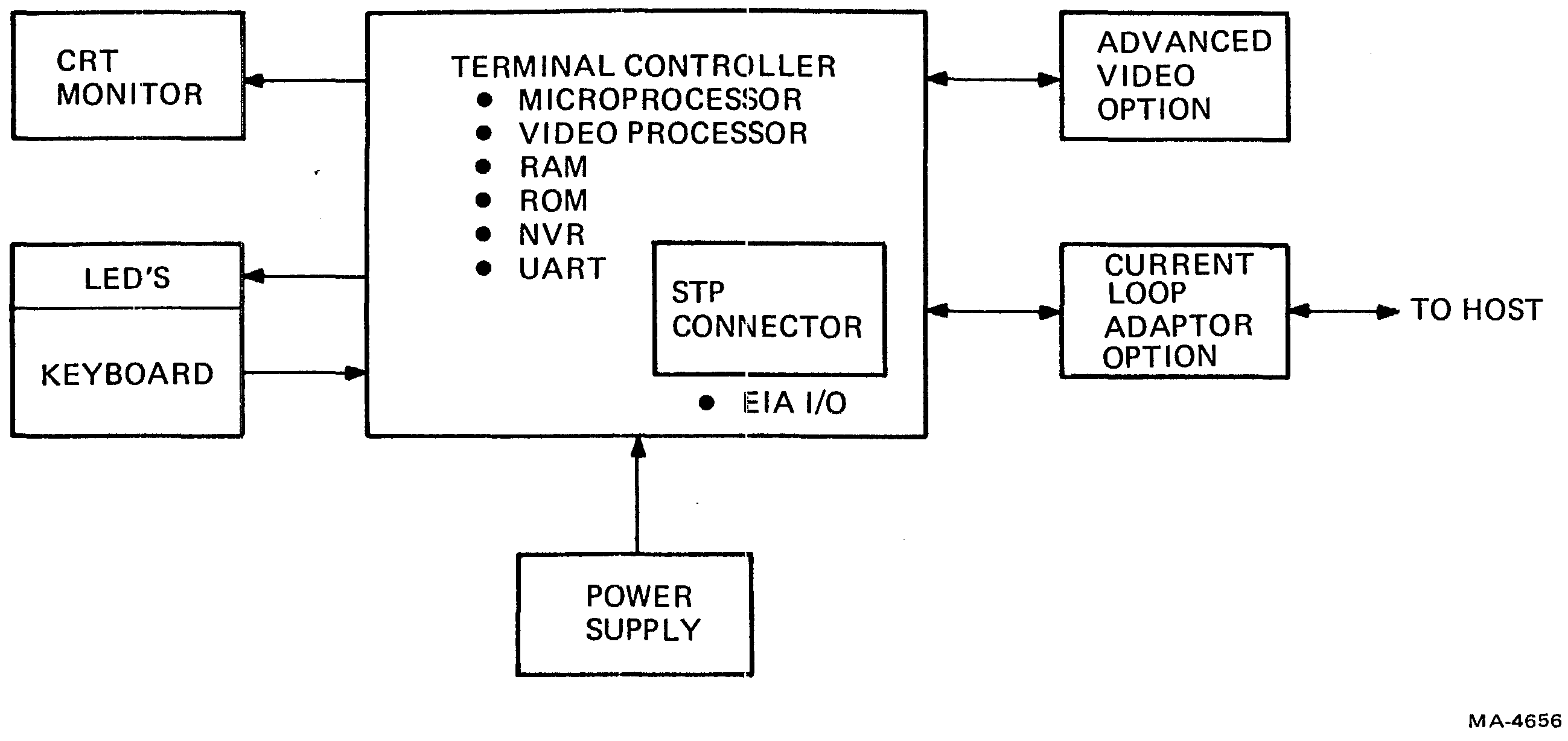

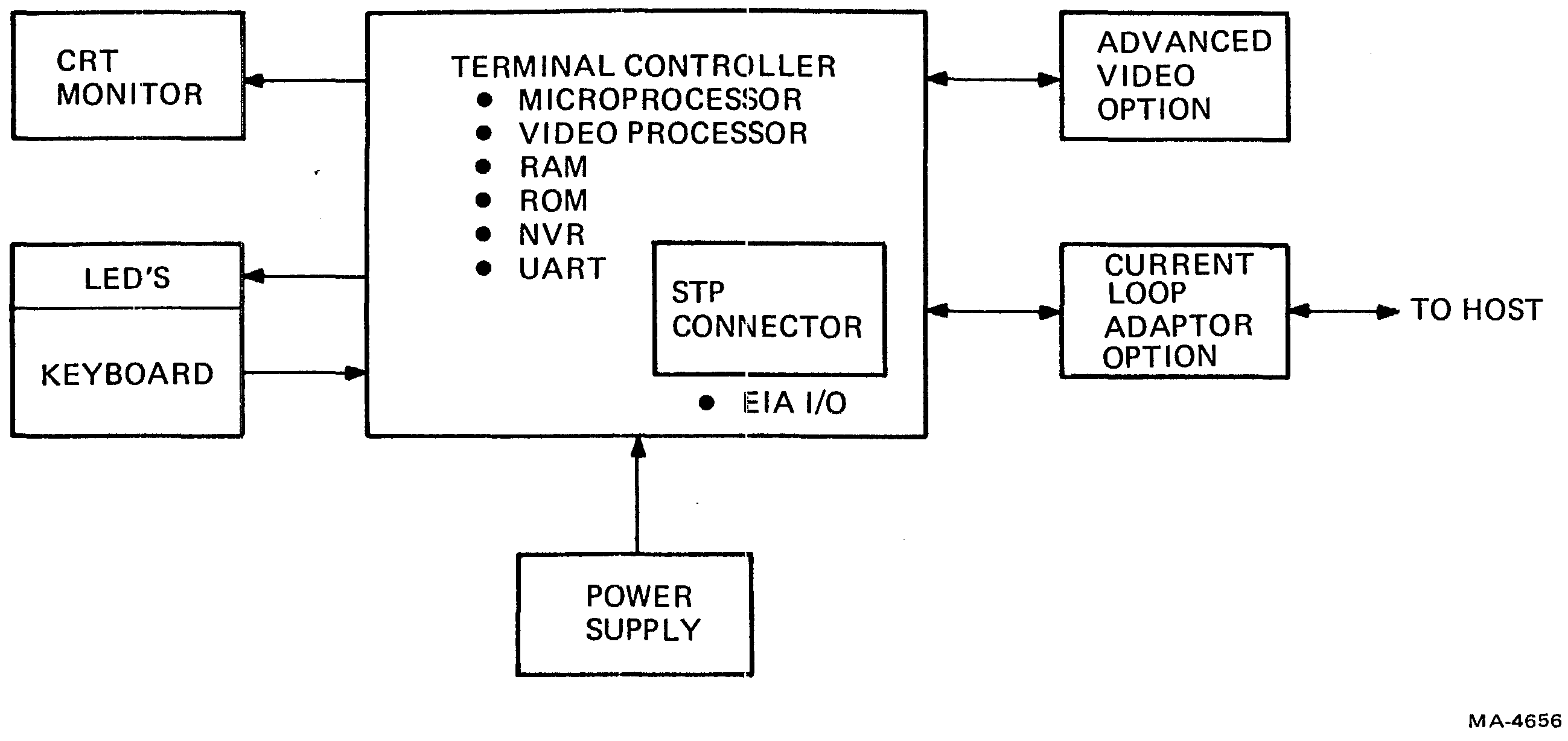

The terminal consists of four basic components (not including enclosures) plus two important options. The components are the terminal controller, the keyboard, the CRT monitor, and the power supply. The options are the advanced video option and the current loop adapter option.

The terminal controller is a single pc board module that manages all displays and all communication. Everything else connects to it. The terminal controller contains these functional components:

The keyboard is the typewriter-style input device for the operator. It has a loudspeaker for user feedback keyclicks and bells, and indicators that show internal states of the terminal.

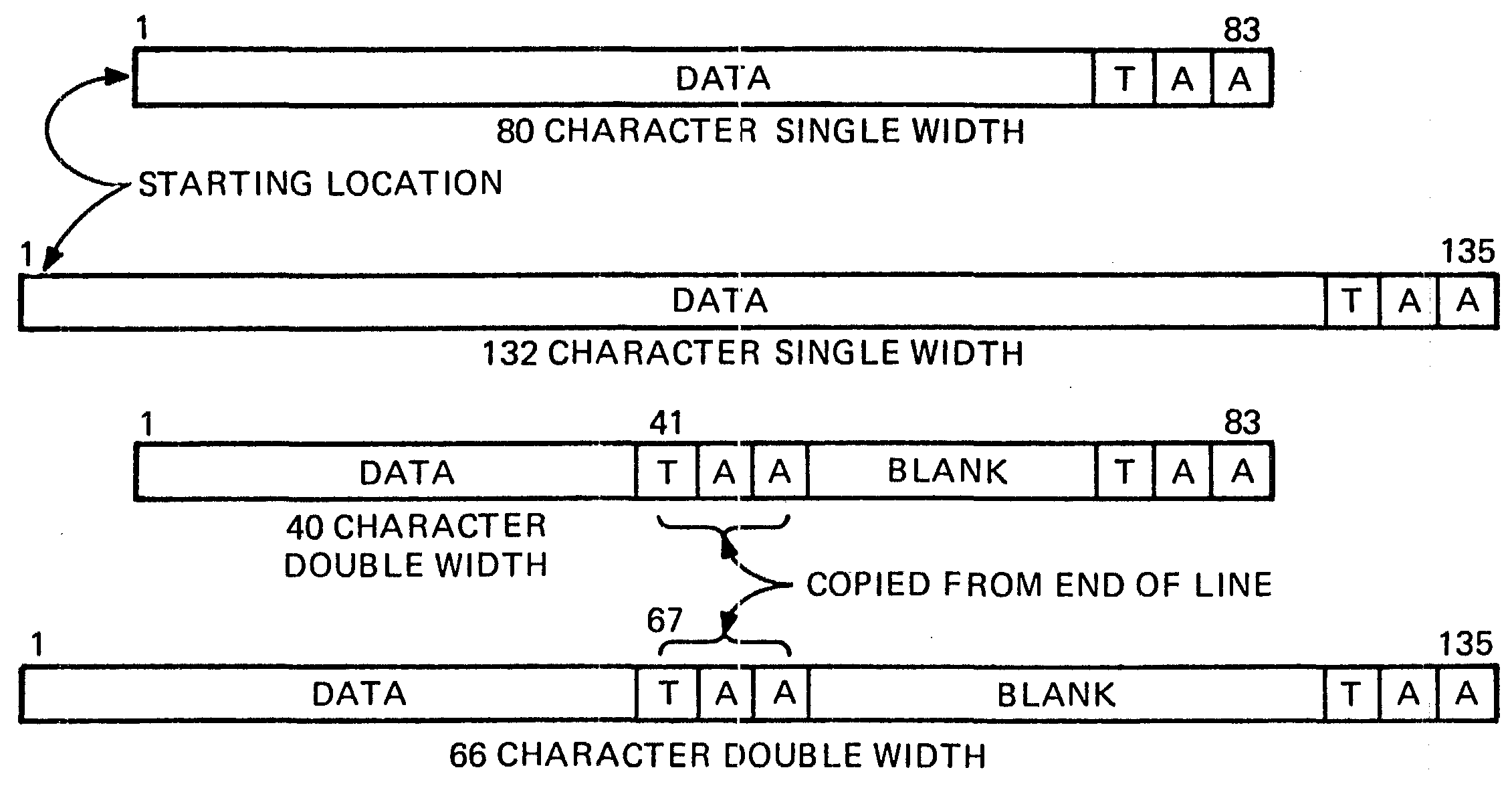

The CRT monitor is a video screen that displays exchanges between the operator and the computer. It can display data in two modes: 80 characters by 24 lines, or 132 characters by 14 lines (or, with the AVO, 132 by 24). With the control circuitry on the terminal controller board, the CRT can perform many special character display functions.

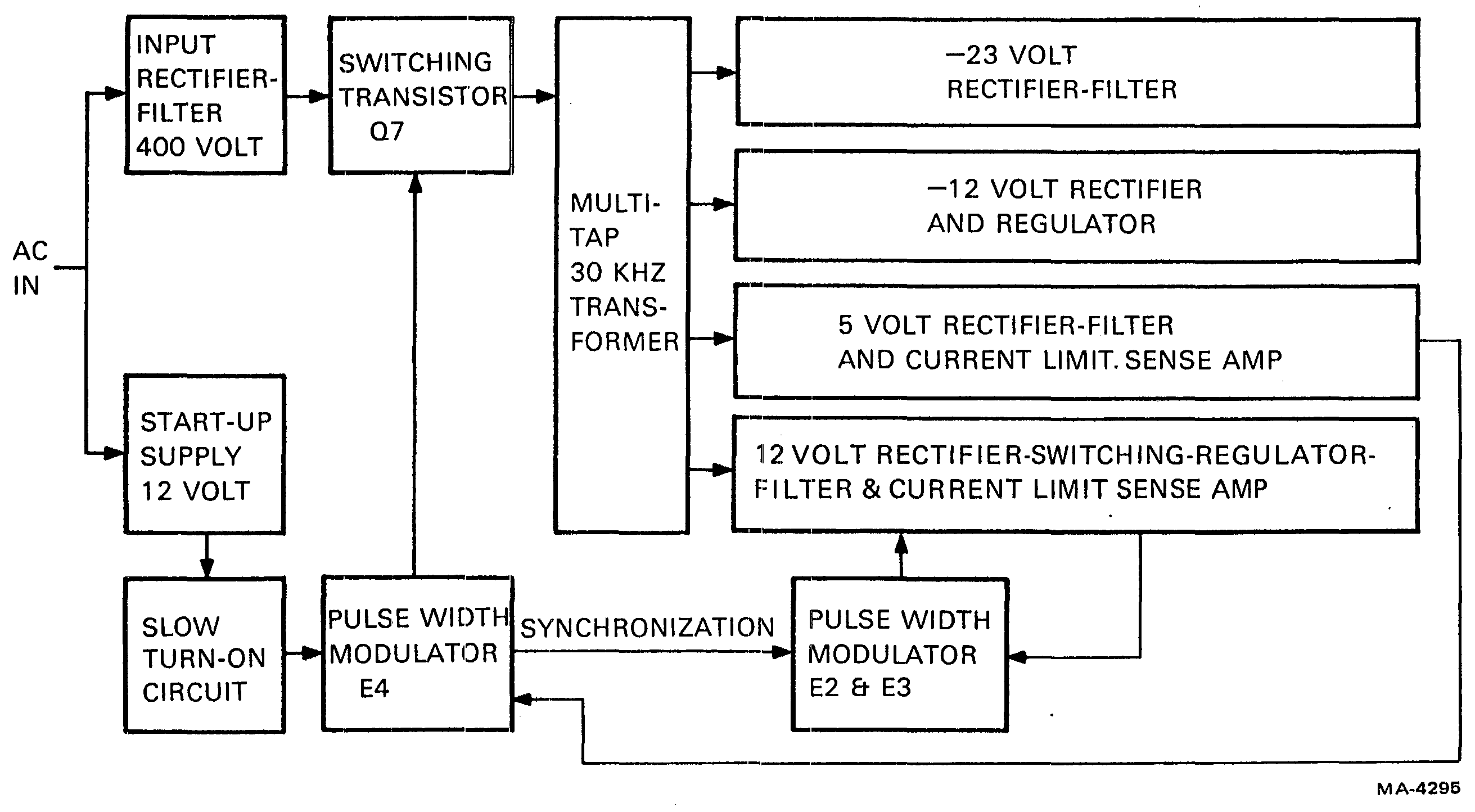

The power supply converts the ac power line to the four dc voltages required by the terminal. It has a switching regulator for highest efficiency and coolest operation.

The advanced video option provides greater display capacity, plus it can carry extra firmware for the expanded functionality of other products in the VT100 series.

The current loop adapter option converts the EIA output of the terminal controller to a more noise immune standard when longer distances between the terminal and the computer are required.

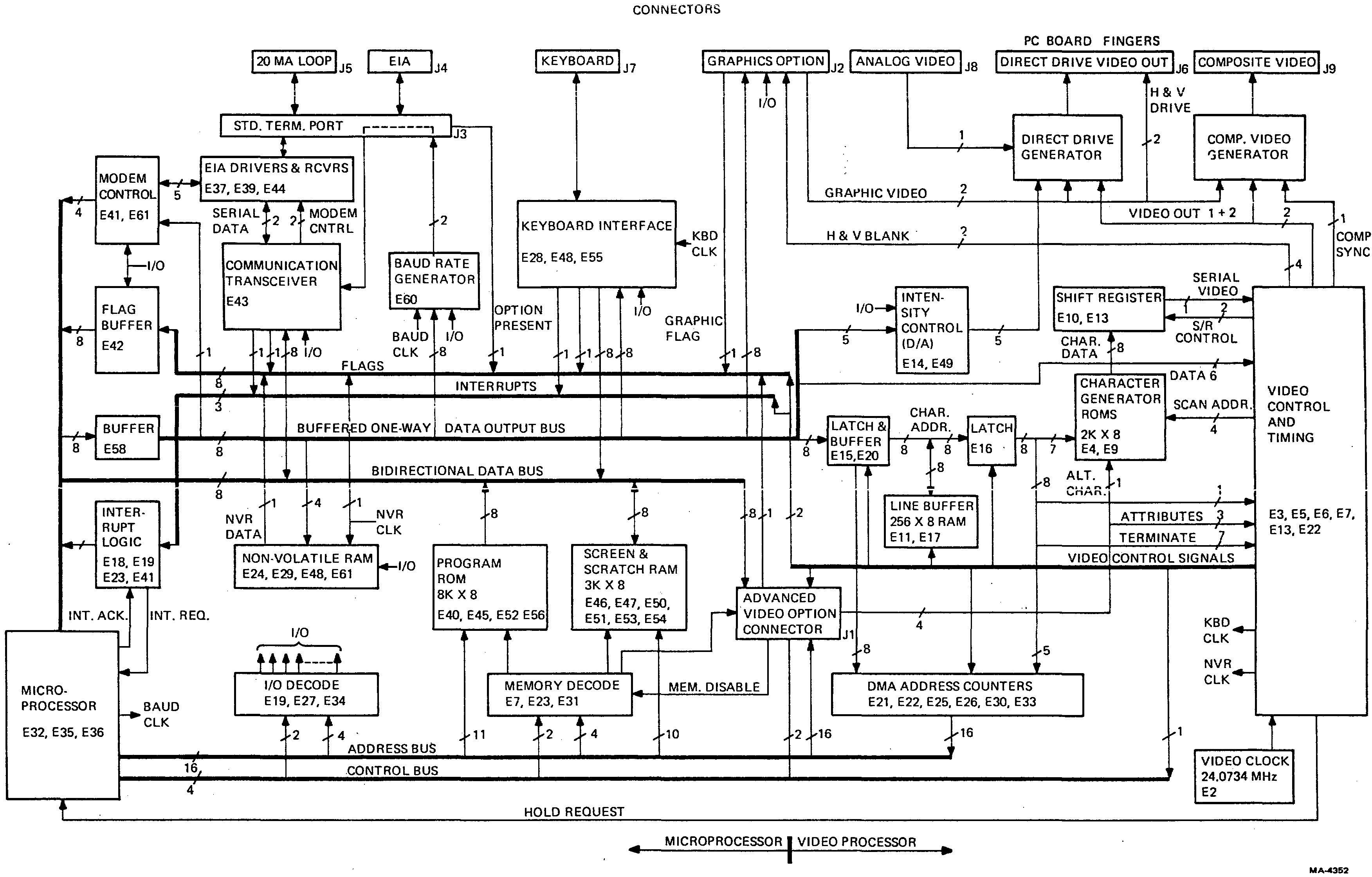

Figure 4-1-2 shows the VT100 terminal as a set of functional blocks. The rest of this section describes these blocks in greater detail.

A microprocessor manages all terminal input and output operations. It also provides the intelligence that enables the VT100 to respond to and generate a wide range of ANSI control functions, and to emulate the characteristics of the VT52. Several of the microprocessor’s program functions are effectively in series with data paths in the terminal. These functions have their own blocks in the functional block diagram to clarify the processes involved. These blocks are shaded to indicate that they are program functions or that the microprocessor controls data transfers between the blocks. The microprocessor is a computer with its instructions in program ROM (read only memory) and working memory in the scratch RAM (random access memory). Terminal parameters for start-up are stored in the nonvolatile RAM (NVR). The advanced video option (AVO) normally contains extra RAM as described below but can also contain extra program ROM.

The VT100 program ROM is an 8K × 8 memory containing instructions and data tables for the terminal’s microprocessor. Memory comes in four 2K packages (later VT100s may have a single 8K package). Checksum data stored in each ROM allows the terminal to confirm the condition of its programming at self-test.

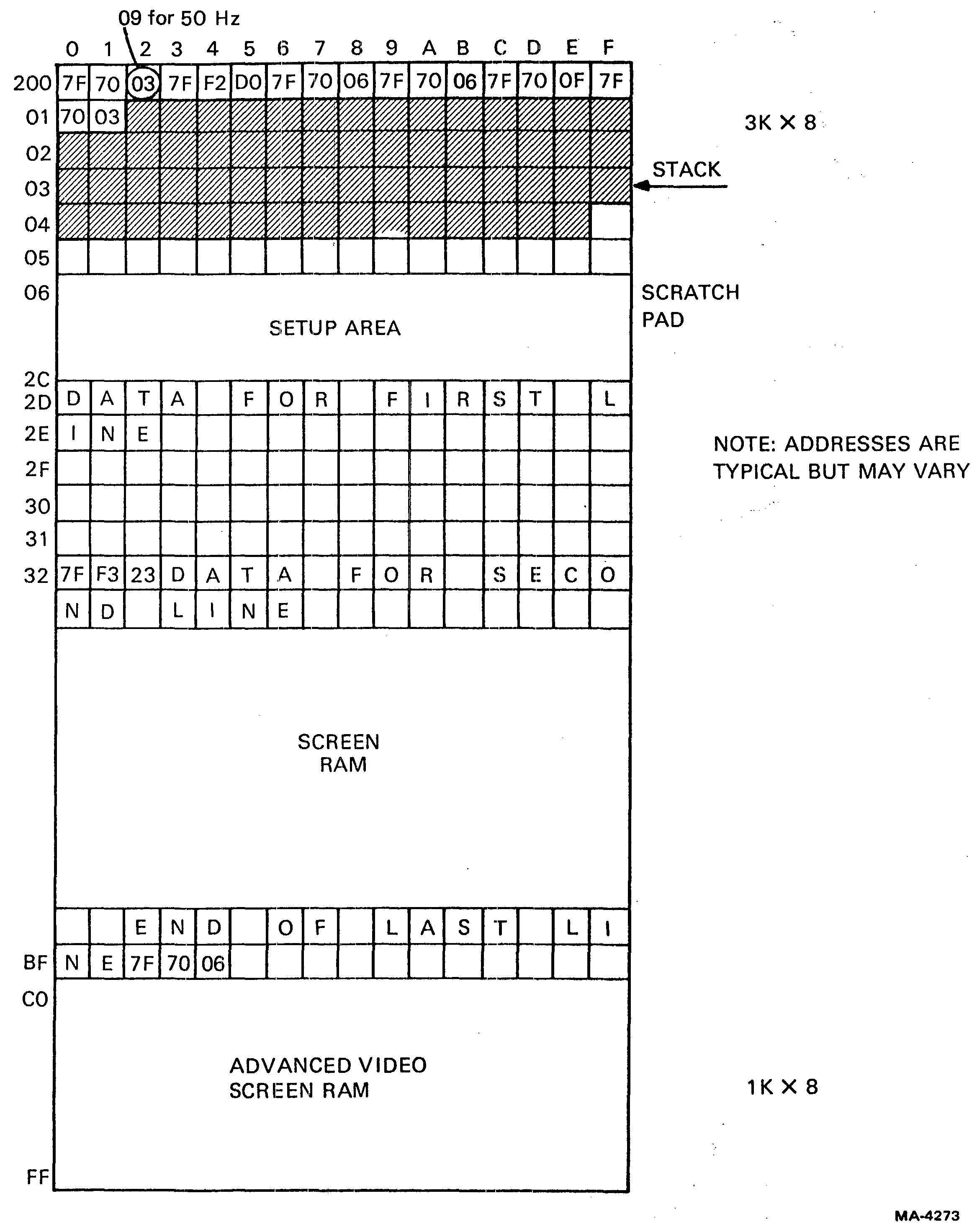

The scratch RAM is the portion of RAM on the terminal controller that is not used for the screen RAM. That is, the RAM is 3K bytes long, but only about 2.3K bytes are used for screen display. The rest of the RAM contains the microprocessor stack, SET-UP data, various flag bytes, the communication SILO, the keyboard buffer, and so on.

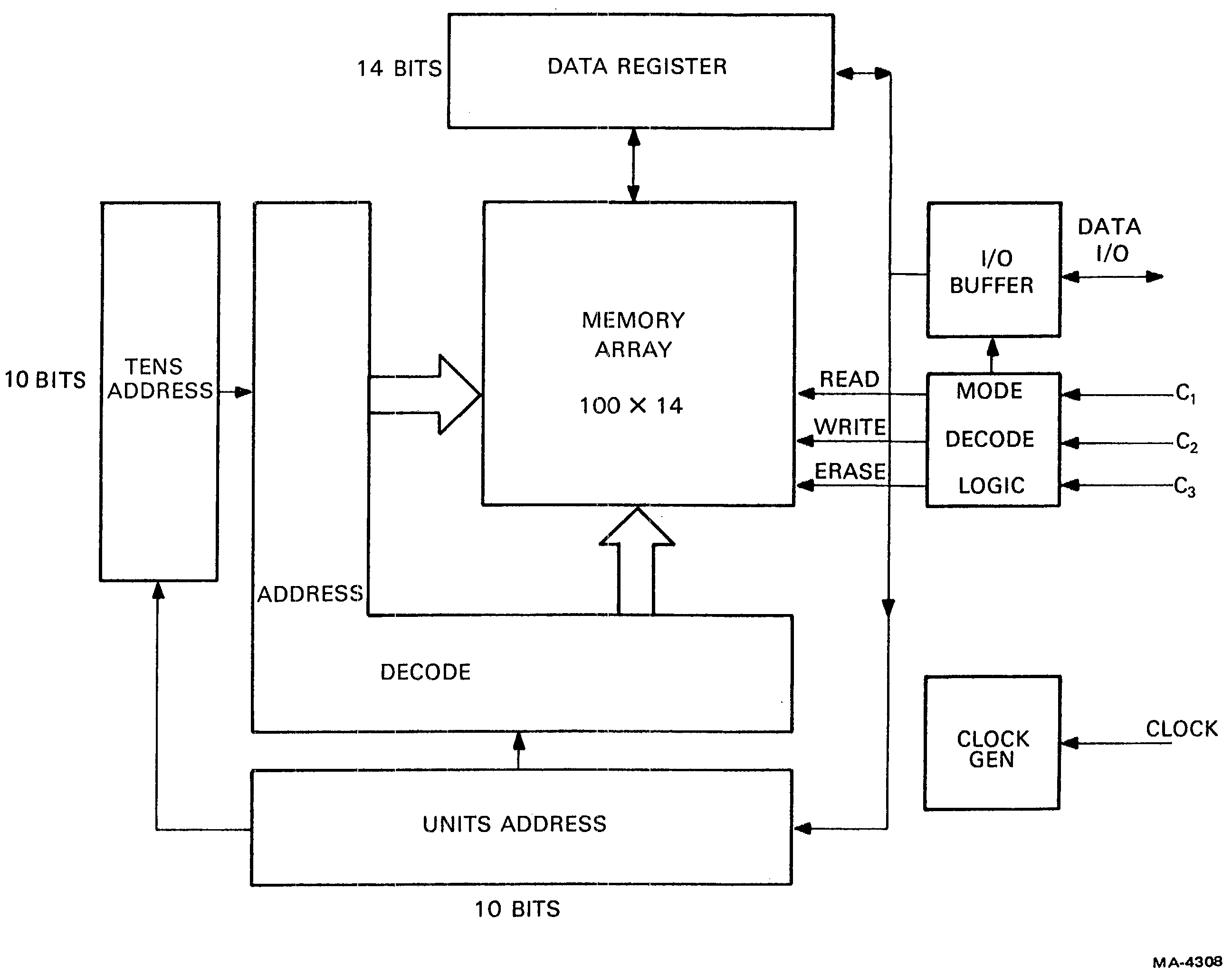

The nonvolatile RAM (NVR) does not lose its data when its power is off. It stores all user-settable features and parameters and the answerback message so that they are available each time the terminal is turned on. Even the screen intensity can be stored. There are no mechanical switches needed for configuration.

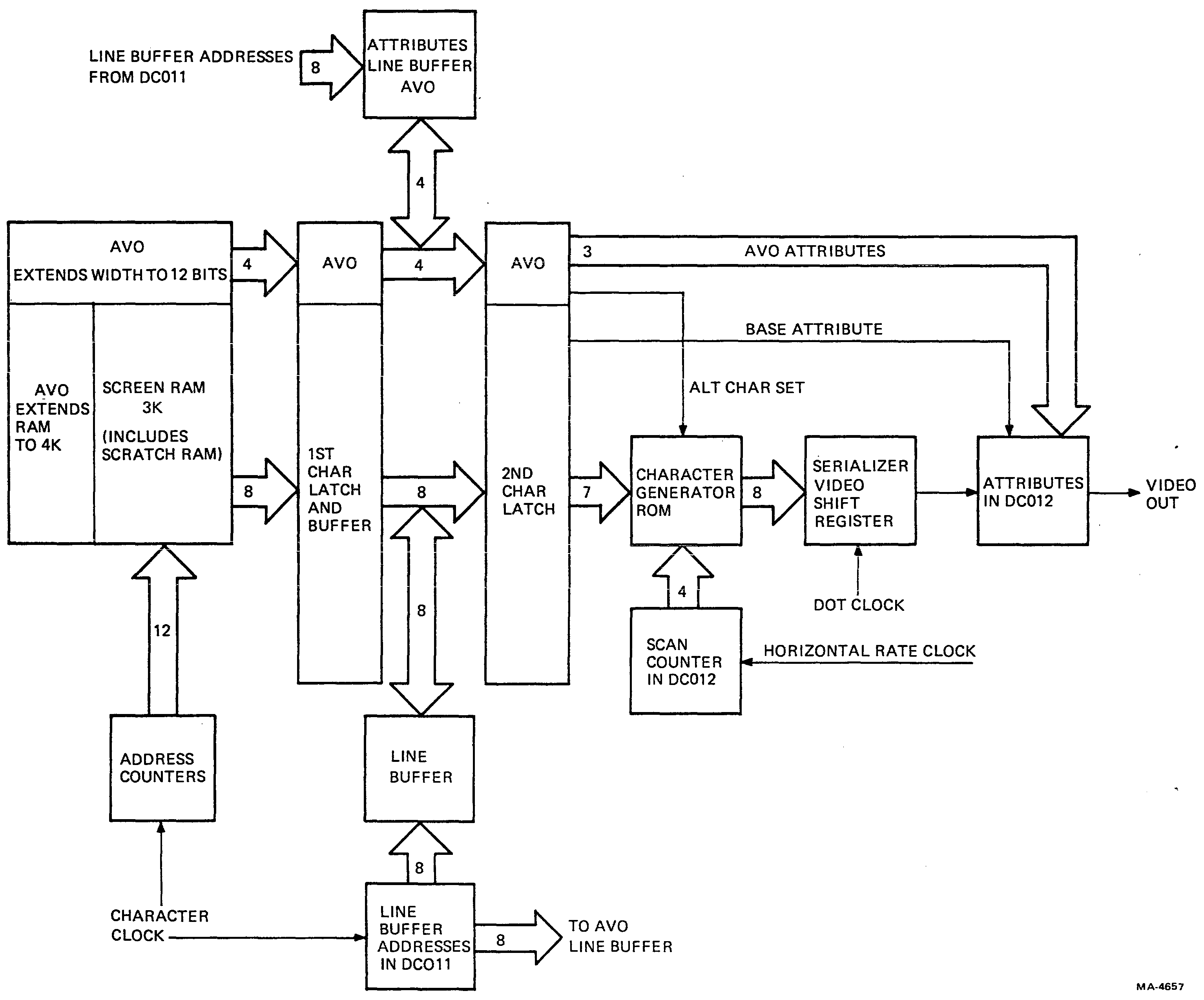

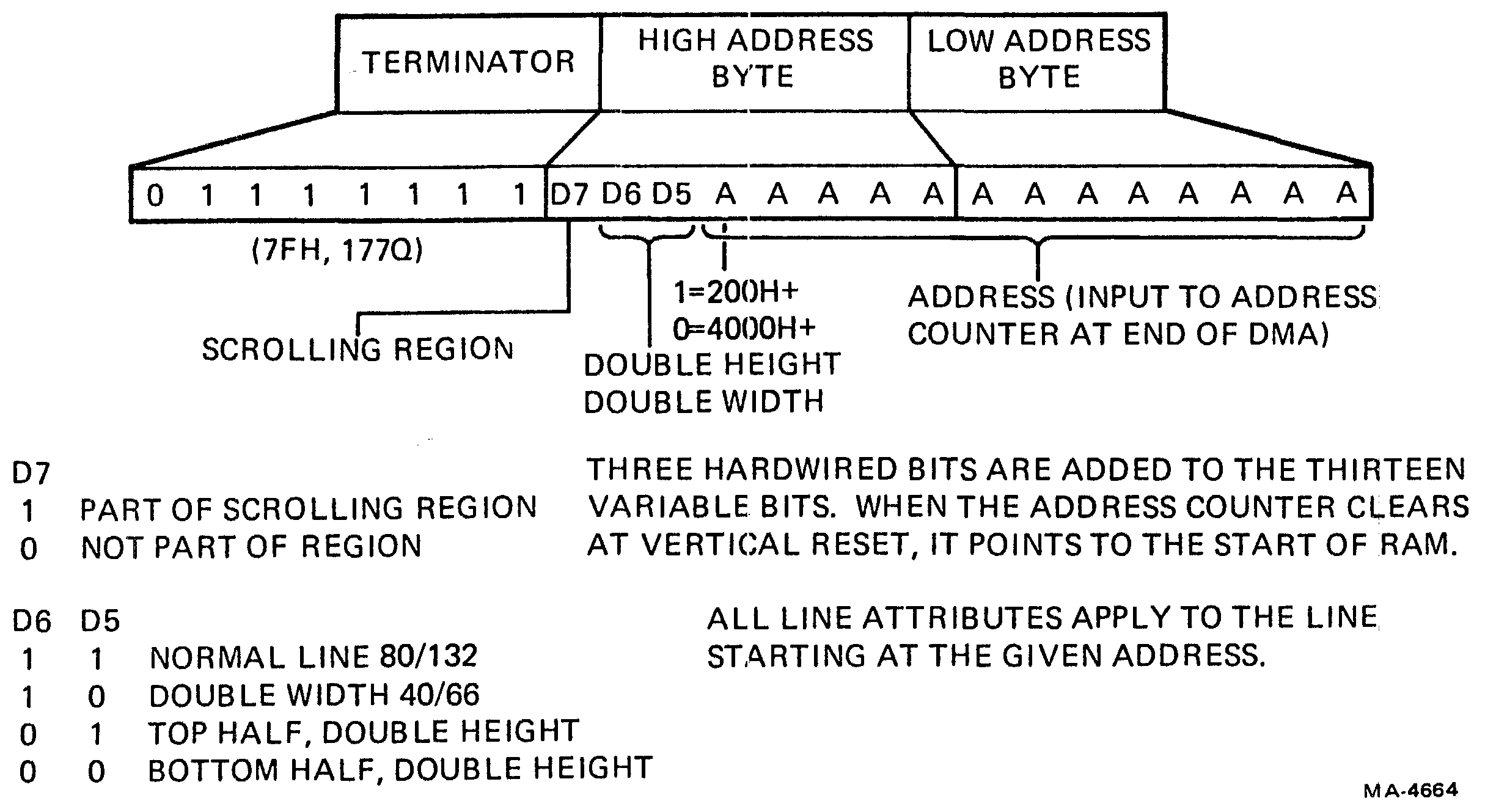

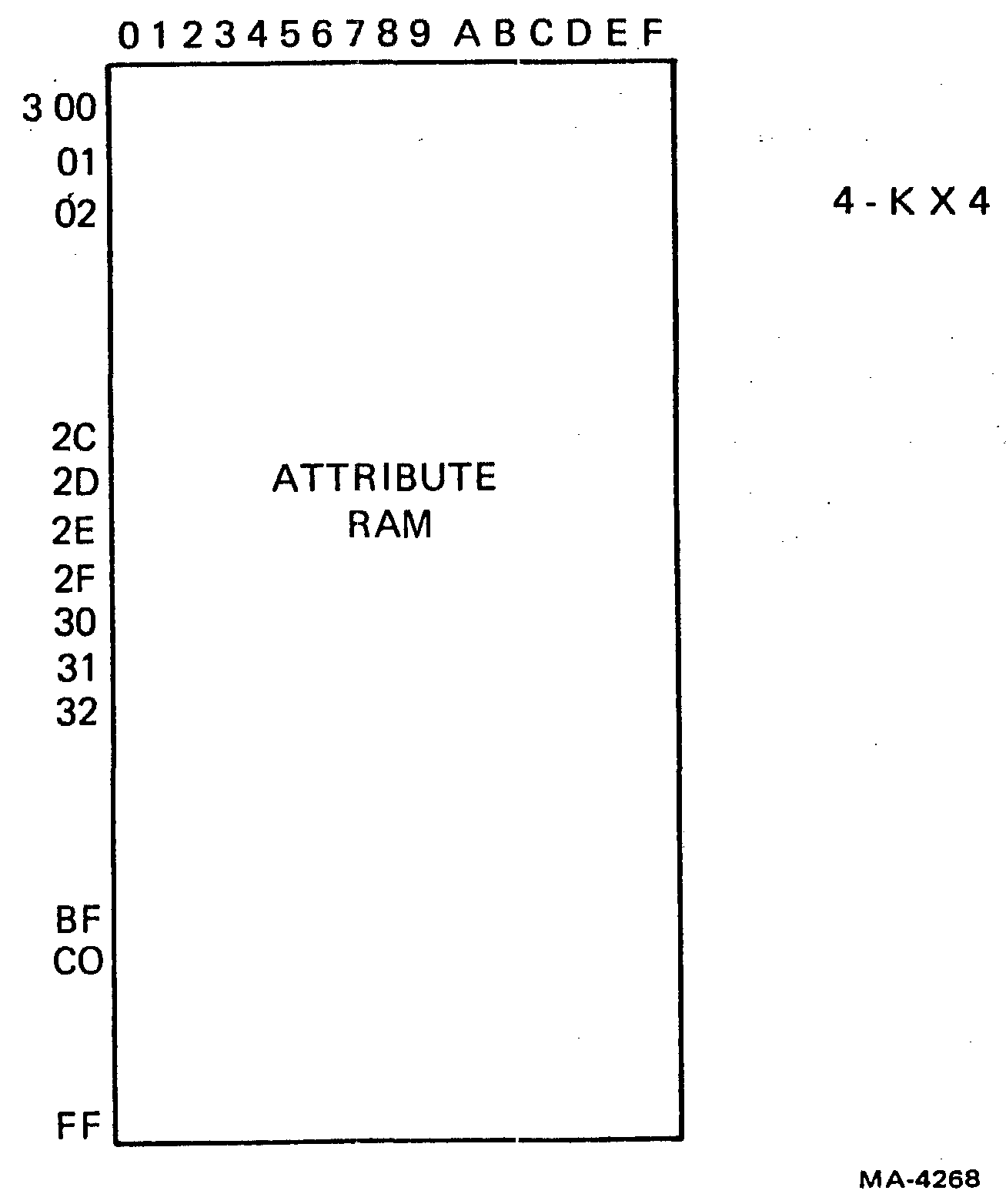

The advanced video option (AVO) contains the 1K × 8 of extra screen RAM needed to expand the display from 14 lines of 132 characters to 24 lines, plus a 4K × 4 RAM to store an extended set of attributes for all characters. The AVO also contains an additional segment of video processor to manage the four extra bits of data. Sockets for ROMs and jumper- or switch-programmable decoders allow expansion or overlay of program memory.

The AVO is a replaceable subunit of the VT100.

The keyboard is the user’s input device to the terminal. The keyboard’s output is a serial data signal that travels along the same wire as data coming from the terminal. The keyboard contains a bidirectional interface circuit, a set of keyswitches arranged like a typewriter, circuits to send the key information to the interface, LED indicators, and a small loudspeaker for keyclicks and bells. The connection to the terminal is a 3-wire coil cord carrying signals, power, and ground.

The keyboard is a replaceable subunit of the VT100.

The terminal can inform the user of some internal conditions such as on-line or local and keyboard locked through the LEDs on the keyboard. The LEDs also may indicate the location of a failure during self test and are user programmable during normal operation.

The output for each key is a number that represents the key’s location (address) in the keyboard switch matrix. The microprocessor’s keyboard translator translates the address to the industry-standard ASCII code.

The ASCII codes wait in a transmit buffer until they can be transmitted. Some keys (such as the numeric keypad in application mode) produce control functions that are three bytes long. The transmit buffer is nine bytes long and thus can store at least three keys of any kind.

The communication transmitter is one-half of a programmable universal synchronous/asynchronous receiver transmitter (PUSART) and its associated circuitry and firmware routines. The PUSART is programmed to place data in a standard asynchronous format by adding control and error detection bits to the original byte. The communication transmitter thus takes the parallel ASCII keycodes out of the keycode buffer, converts them to serial form, and delivers them to the EIA interface.

Data that the host sends to the terminal enters the communication receiver which is the other half of the PUSART. The PUSART accepts serial data from the interface and converts it to parallel form. The PUSART also checks for errors and records them in a status byte. The microprocessor reads the data and then the status byte to confirm the correctness of the data. If an error is detected, a checkerboard is displayed instead of a character to symbolize the error. If the microprocessor is busy managing the display, it devotes only enough time to the communication receiver to get the incoming code and check it for special codes requiring immediate action.

The rest of the incoming codes are stored in a part of RAM memory called a SILO. This memory maintains the order of the data as it arrives; the first data to arrive leaves first. This memory gives incoming data a place to wait when the microprocessor cannot transfer data from the communication receiver to the screen RAM as fast as it arrives. The SILO control routine checks the filling of the SILO and can issue XON and XOFF commands to the host to try to keep from overfilling. (XON and XOFF are explained in Section 4.3, Communication.)

In local mode, data from the keyboard bypasses the communication receiver and transmitter and the SILO.

When the microprocessor has enough time, it takes data from the SILO and puts it through a control function parser routine in the microprocessor. Each code is tested to see if it is in the control range (<20H or 7FH). If it is, the microprocessor acts on it immediately. Line feed, for example, causes a one line scroll. If the code is 1BH (escape), more codes are read from the SILO until the characters that define a control function are seen. Then the microprocessor executes the control function immediately or discards it if it is not a valid function. Noncontrol codes are ignored by the parser and are written into the screen RAM.

The screen RAM is a memory that stores data for display on the screen (CRT monitor). The memory is organized according to the SET-UP line length specifications. Basic terminal memory can hold 24 lines of 80 characters or 14 lines of 132 characters. With the extra memory provided by the advanced video option, the screen size may increase to 24 lines of 132 characters and four additional bits are appended to each character location to allow expanded character attributes. (A character attribute modifies the display of that character relative to the preset values for the entire screen.)

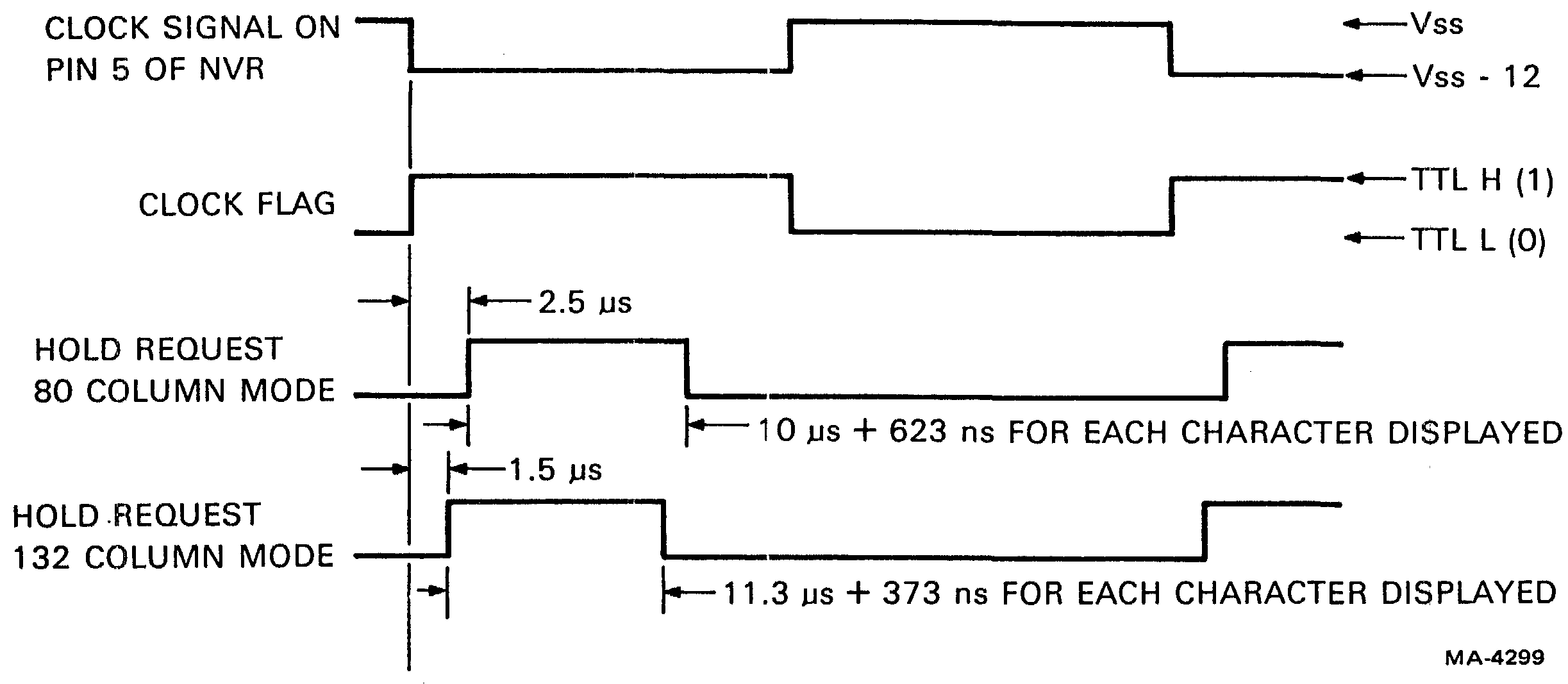

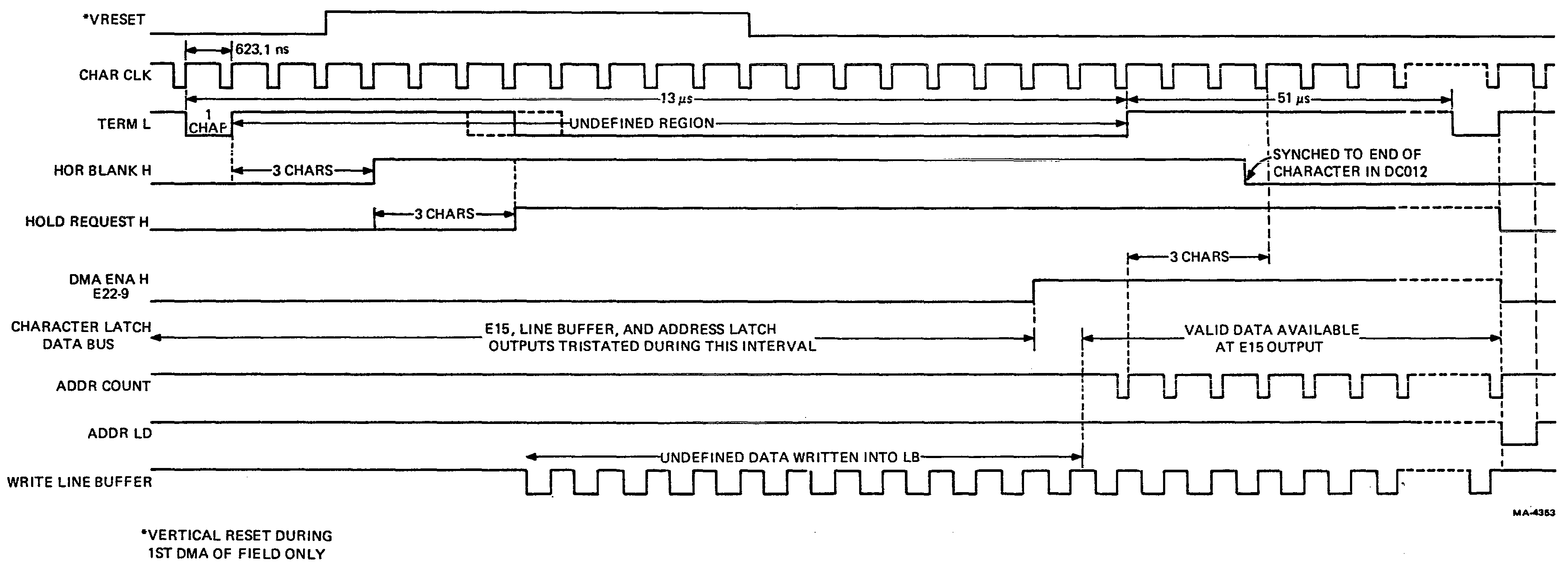

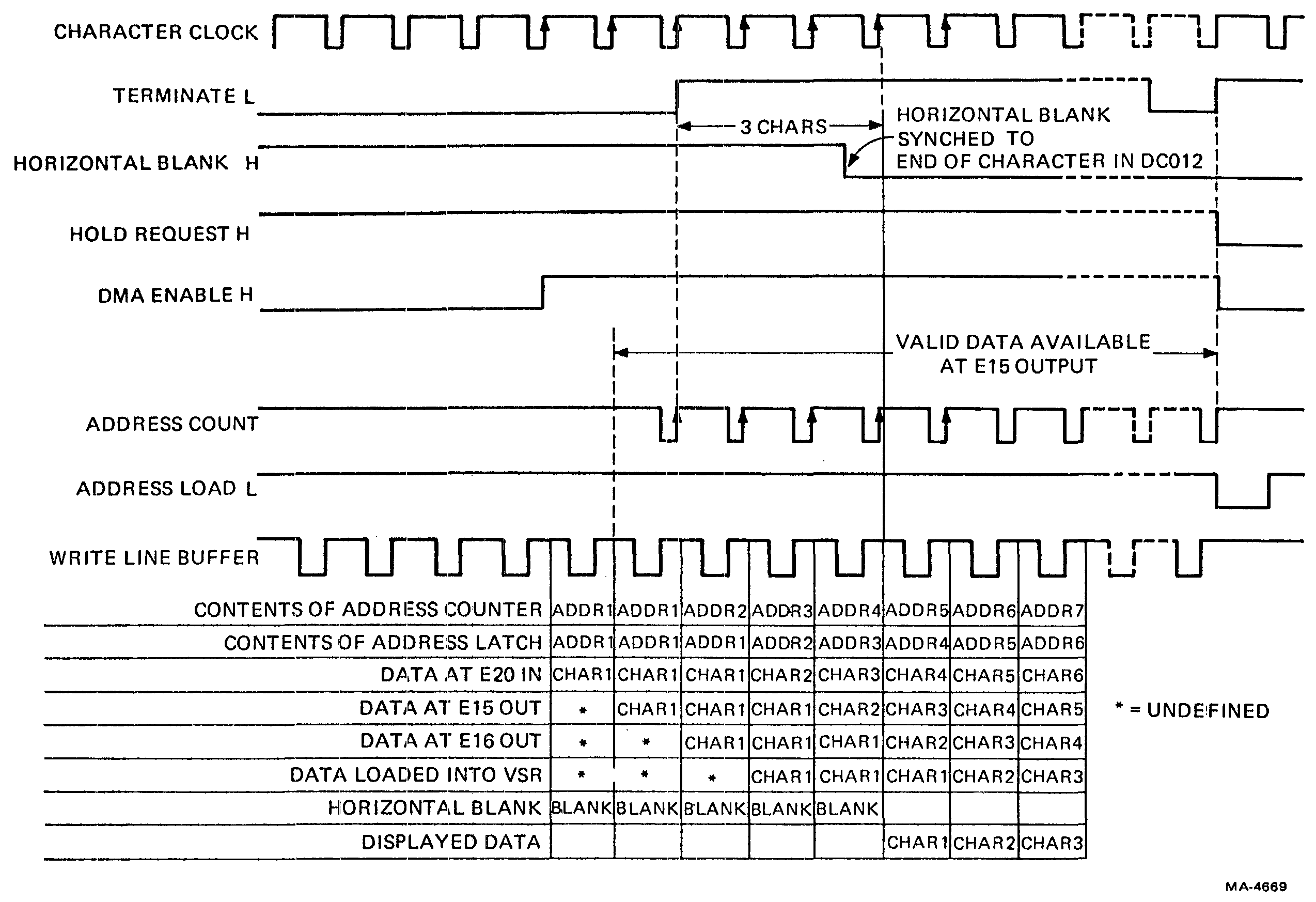

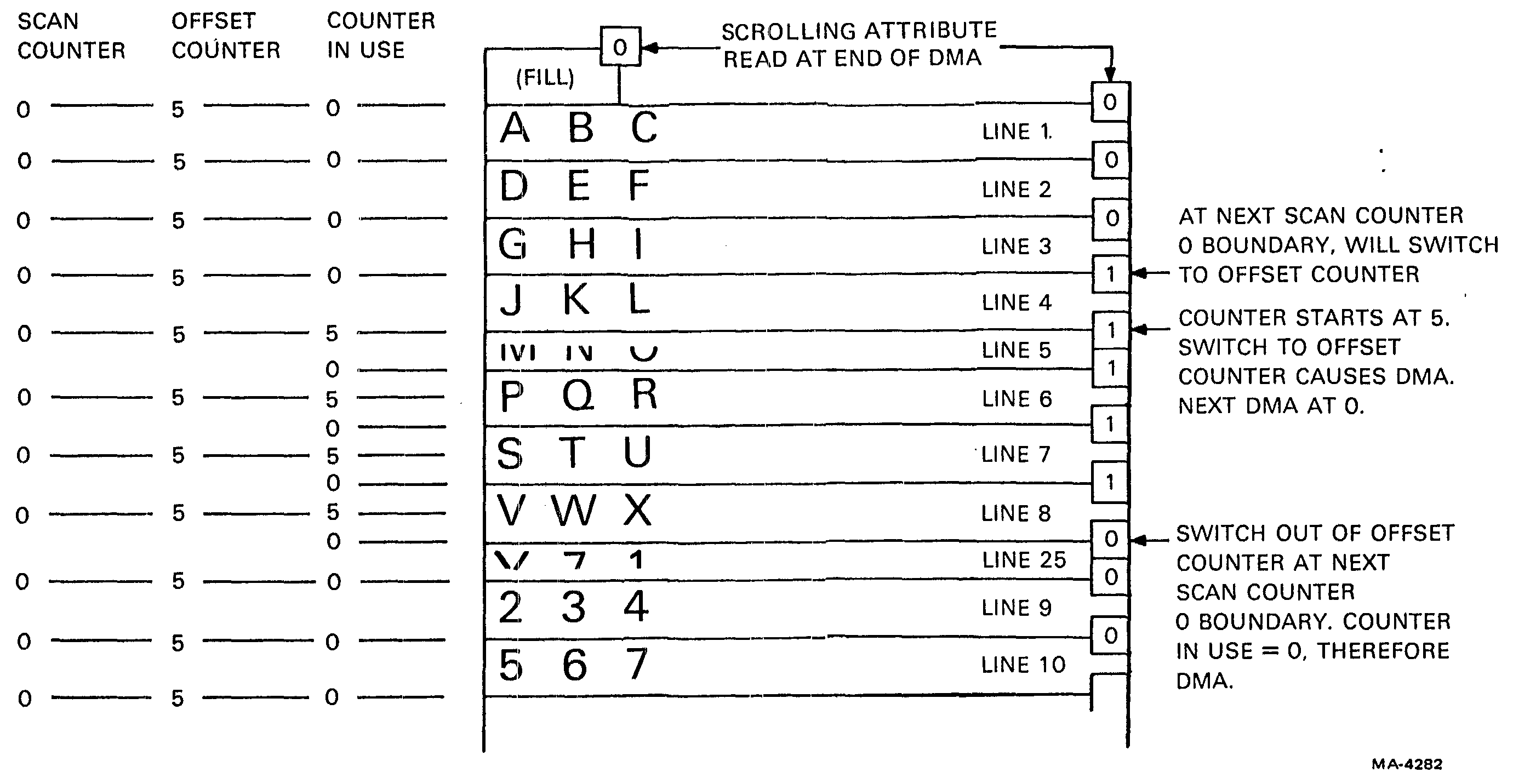

Most of the time, the screen RAM is readable and writable by the microprocessor. For about 10 percent of the time, during the first scan of each 10 scan line of characters, the video processor silences the microprocessor and takes full control of the screen RAM, providing its own addresses to access the memory. This complete control of memory (by a device other than the microprocessor, which is normally in control) is called a direct memory access (DMA). The DMA allows fast access of data in memory because the microprocessor does not have to perform all the steps of addressing, reading, and writing to a destination. The video processor needs the fast access because the data rate required to display a line of characters on the CRT is greater than the microprocessor can handle.

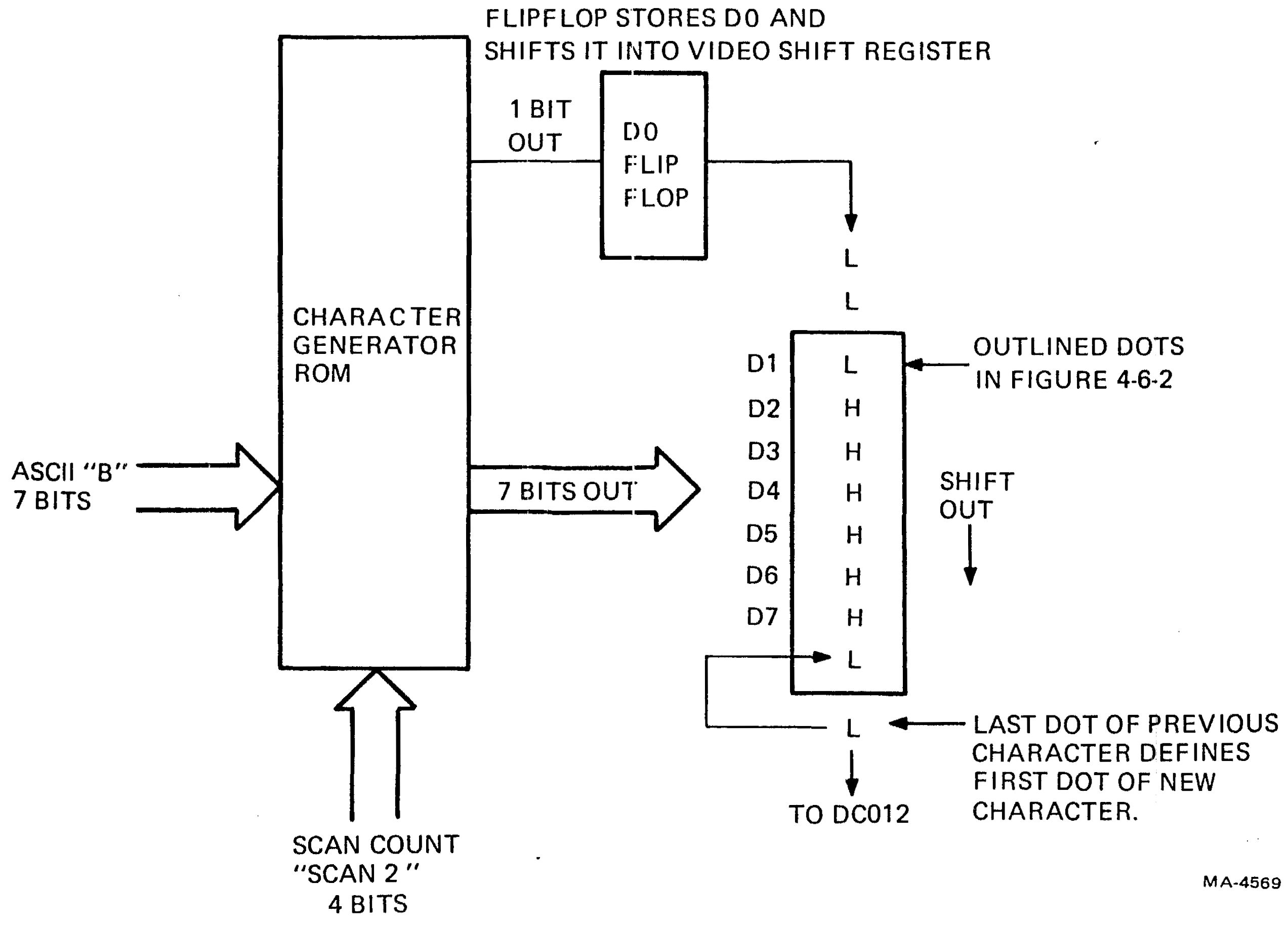

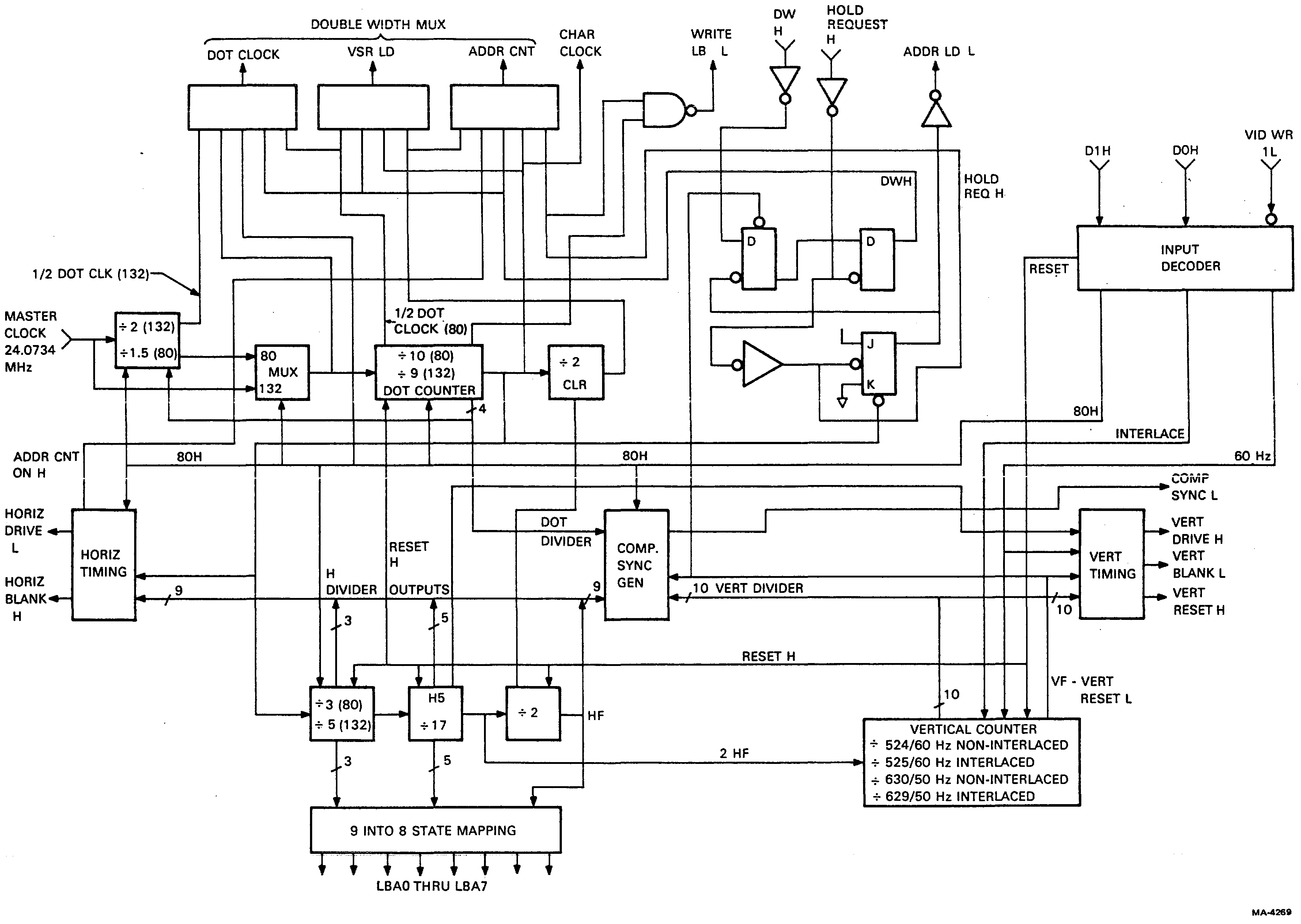

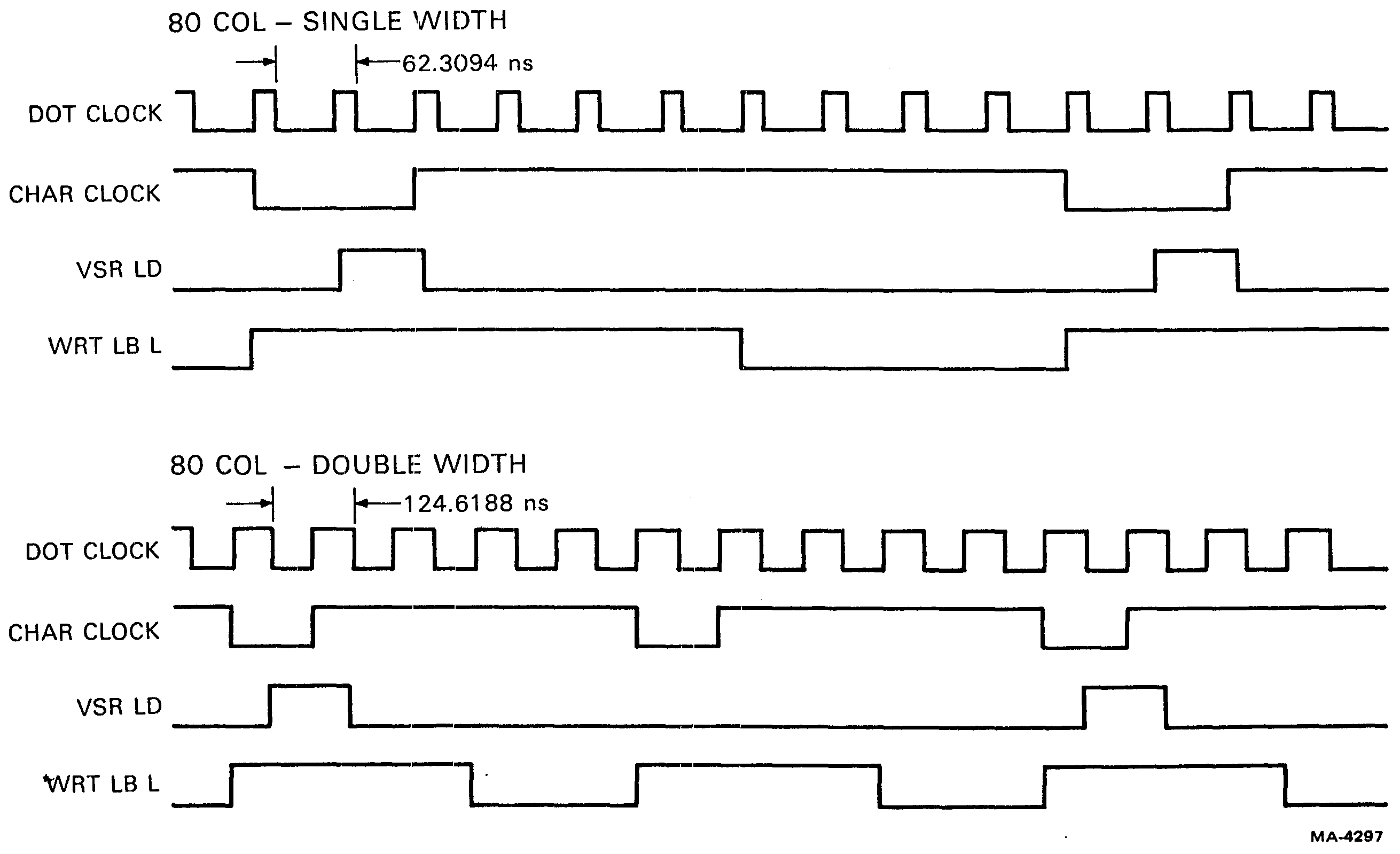

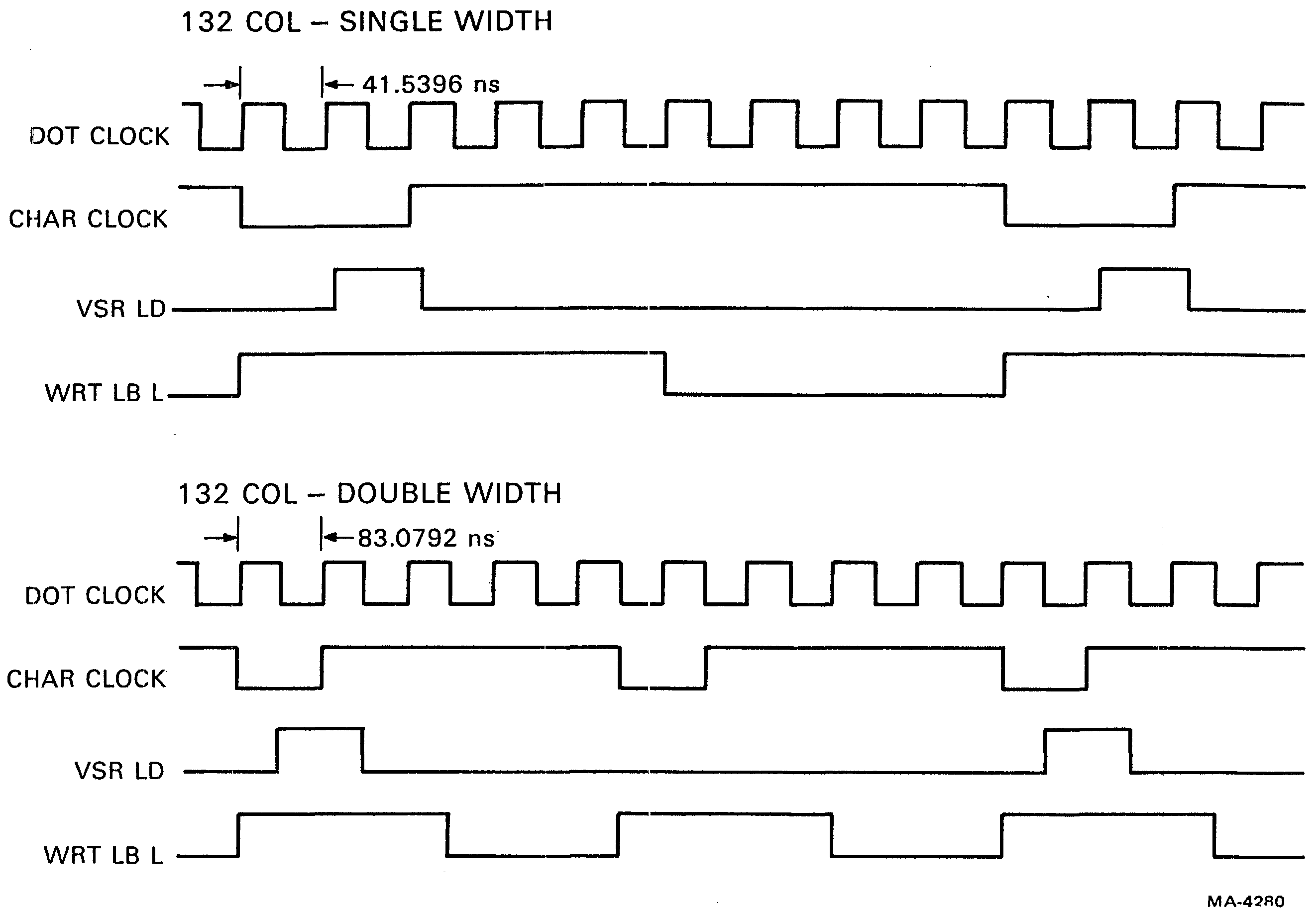

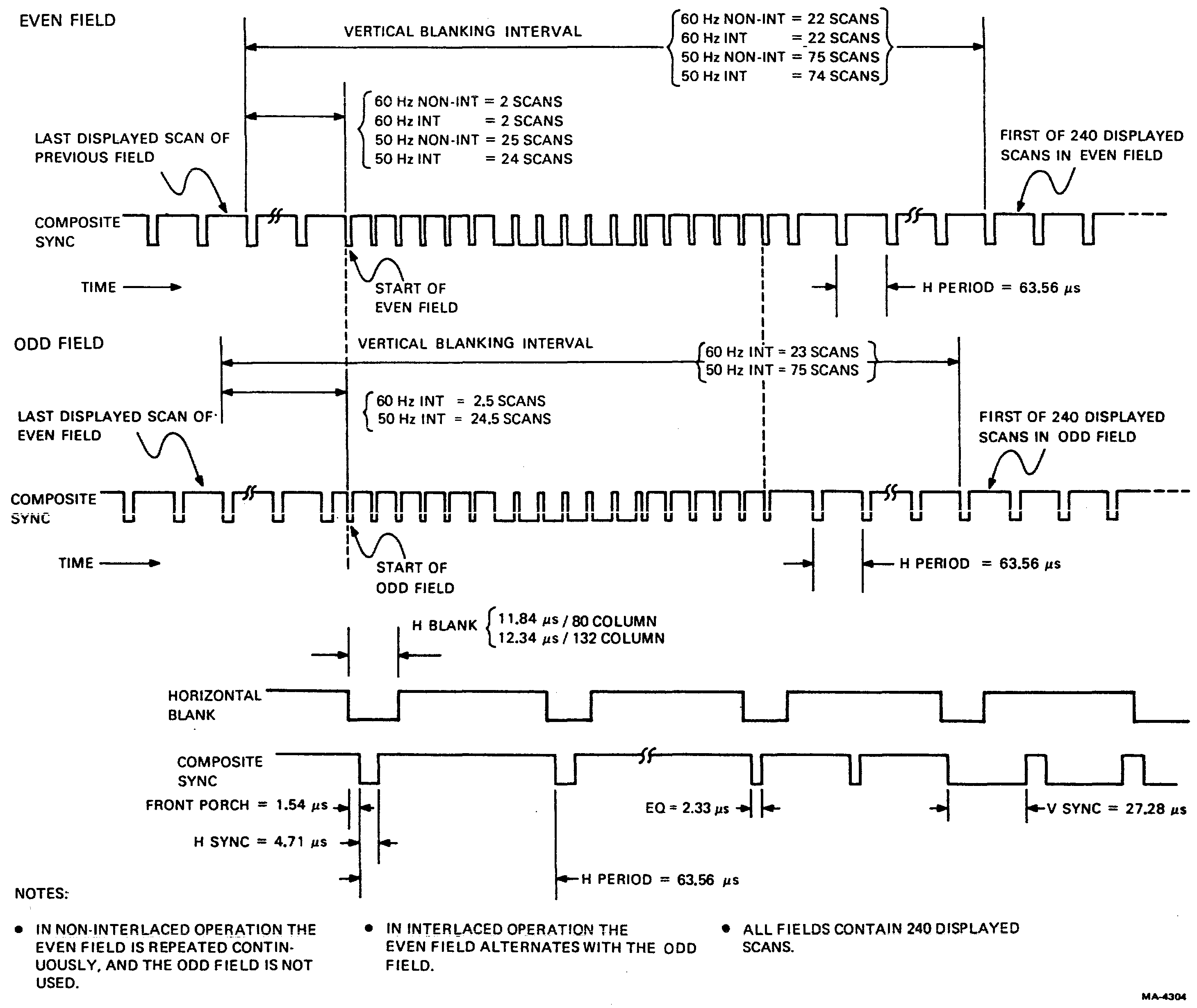

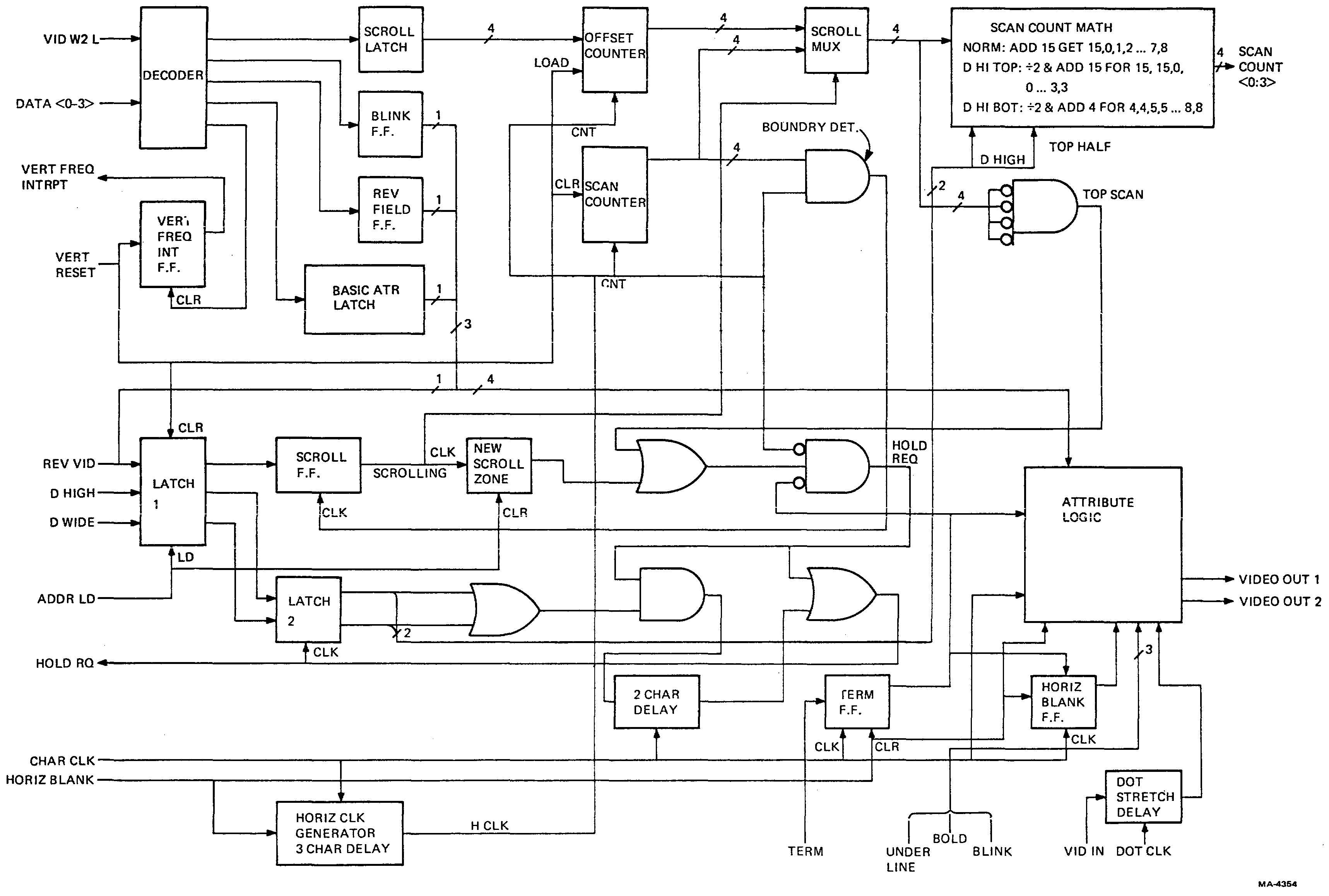

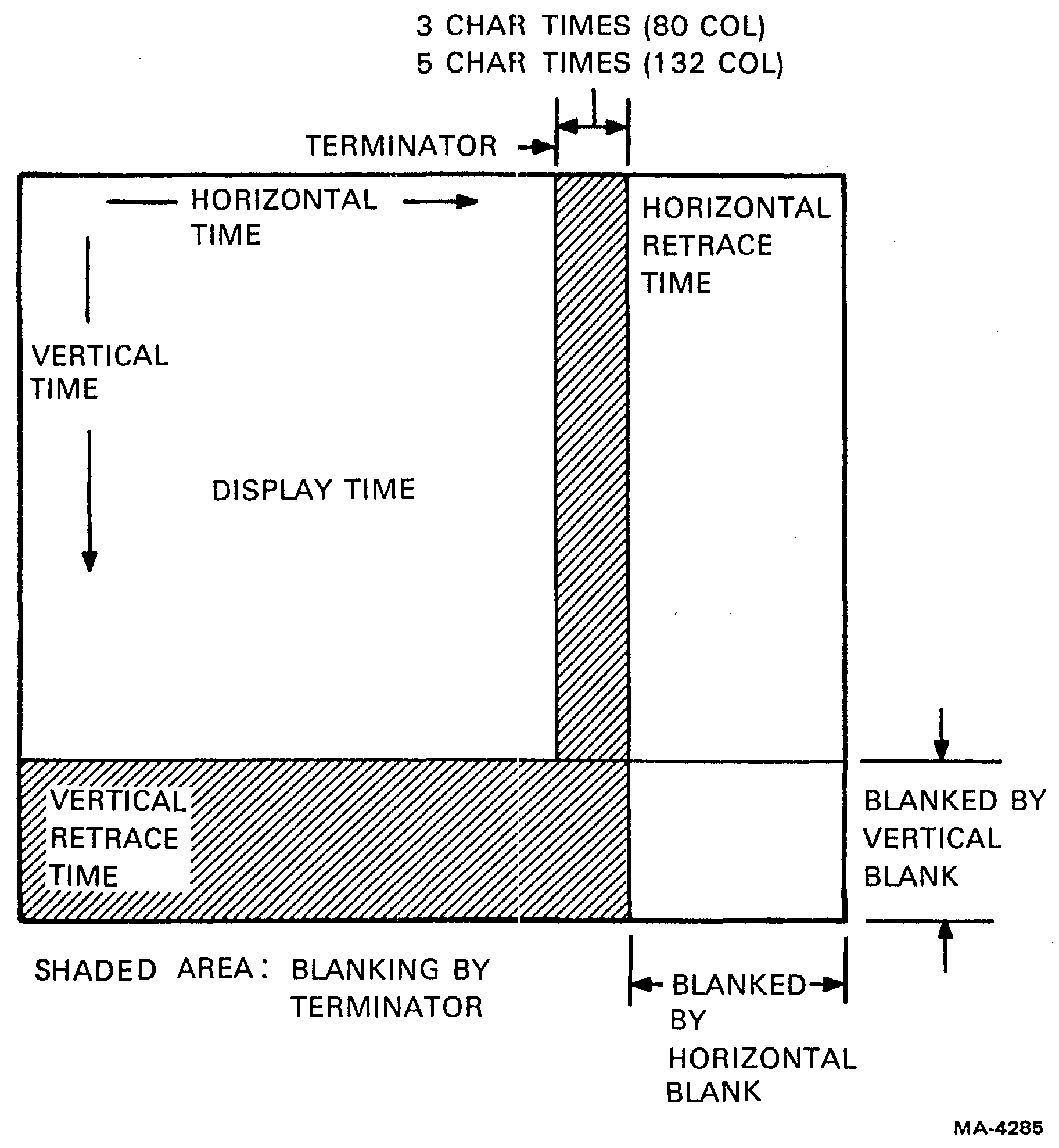

The microprocessor puts displayable data in the screen RAM, The video processor direct memory accesses (DMAs) data a line at a time from the RAM. It converts the ASCII-encoded data into streams of pulses which, when converted to light on a CRT screen, appear to form characters on the screen. Custom ICs provide the complex timing and control signals required for this conversion. The video processor can be programmed by the user to perform the conversion at different rates (called refresh rates) to minimize flicker at different power line frequencies. A number of other aspects of video processor operation can be programmed as well.

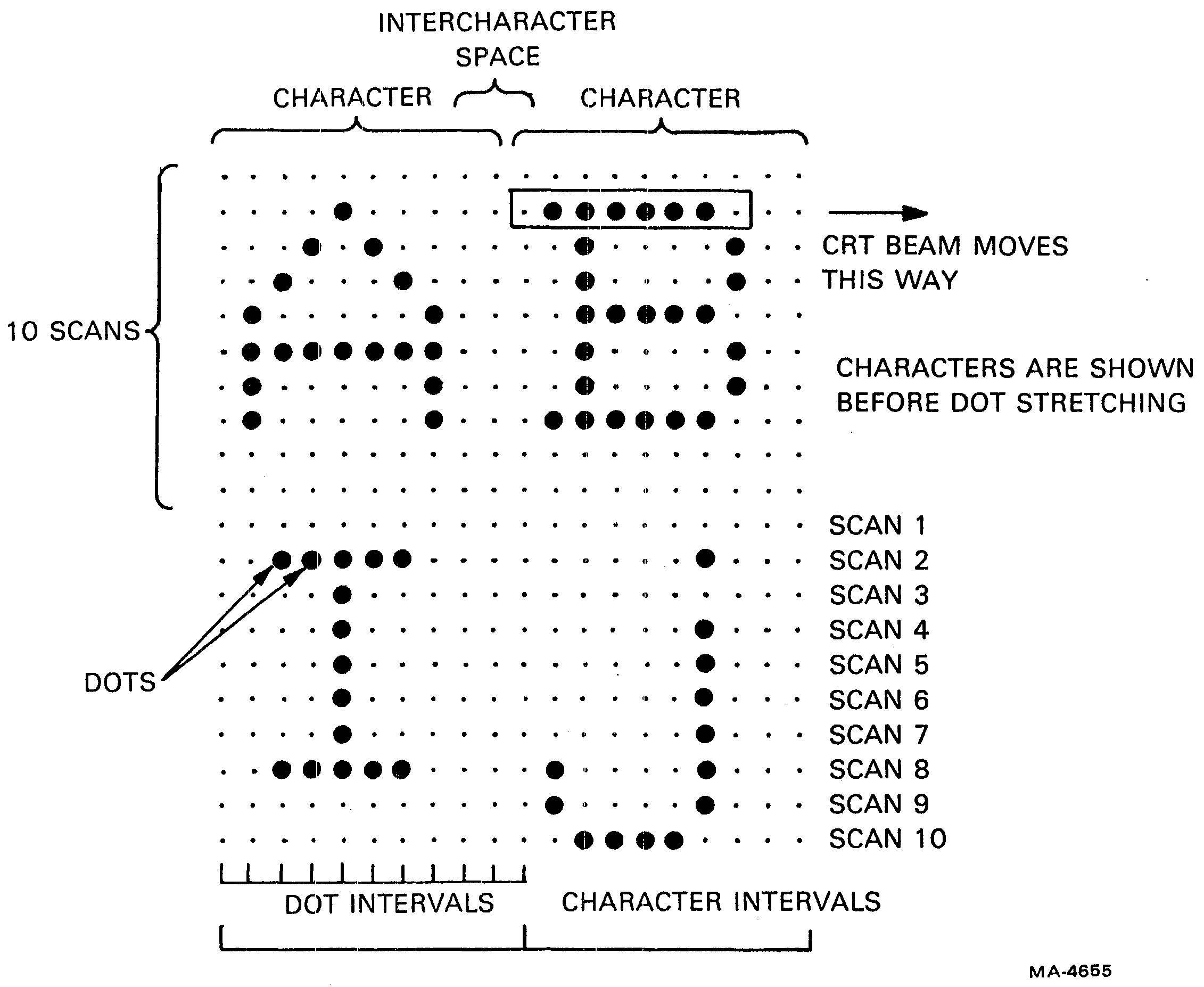

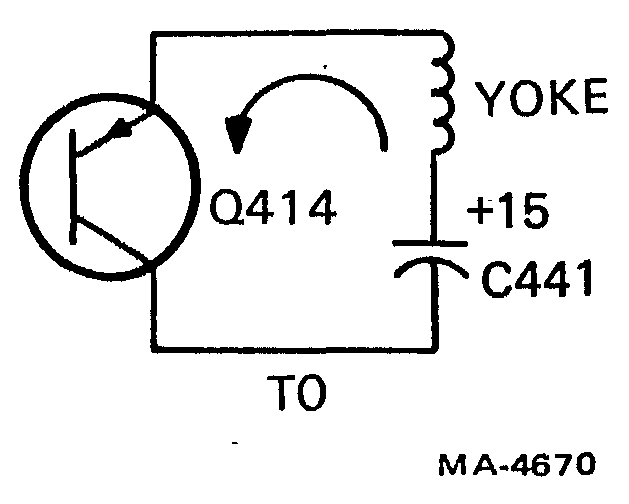

The cathode ray tube (CRT) monitor is a simplified monochrome television set. It converts electrical pulse streams into dots of light by exciting a phosphor on the face of the tube with a moving electron beam. A video input from the video processor enters a cathode drive circuit that regulates the strength of the electron beam. The cathode driver is a linear amplifier that allows the CRT to display different intensities (gray scale). The monitor uses timing pulses from the video processor to drive the horizontal and vertical electron beam deflection circuits. These circuits cause the beam to travel down the screen slowly while rapidly moving sideways to draw horizontal traces called scans. This beam movement produces a pattern which is called a raster and the display system is called raster scanning. Because the beam repeatedly passes by each location on the screen, the video processor, by synchronizing its output with the motion of the beam, can make rows of dots of light align to form characters.

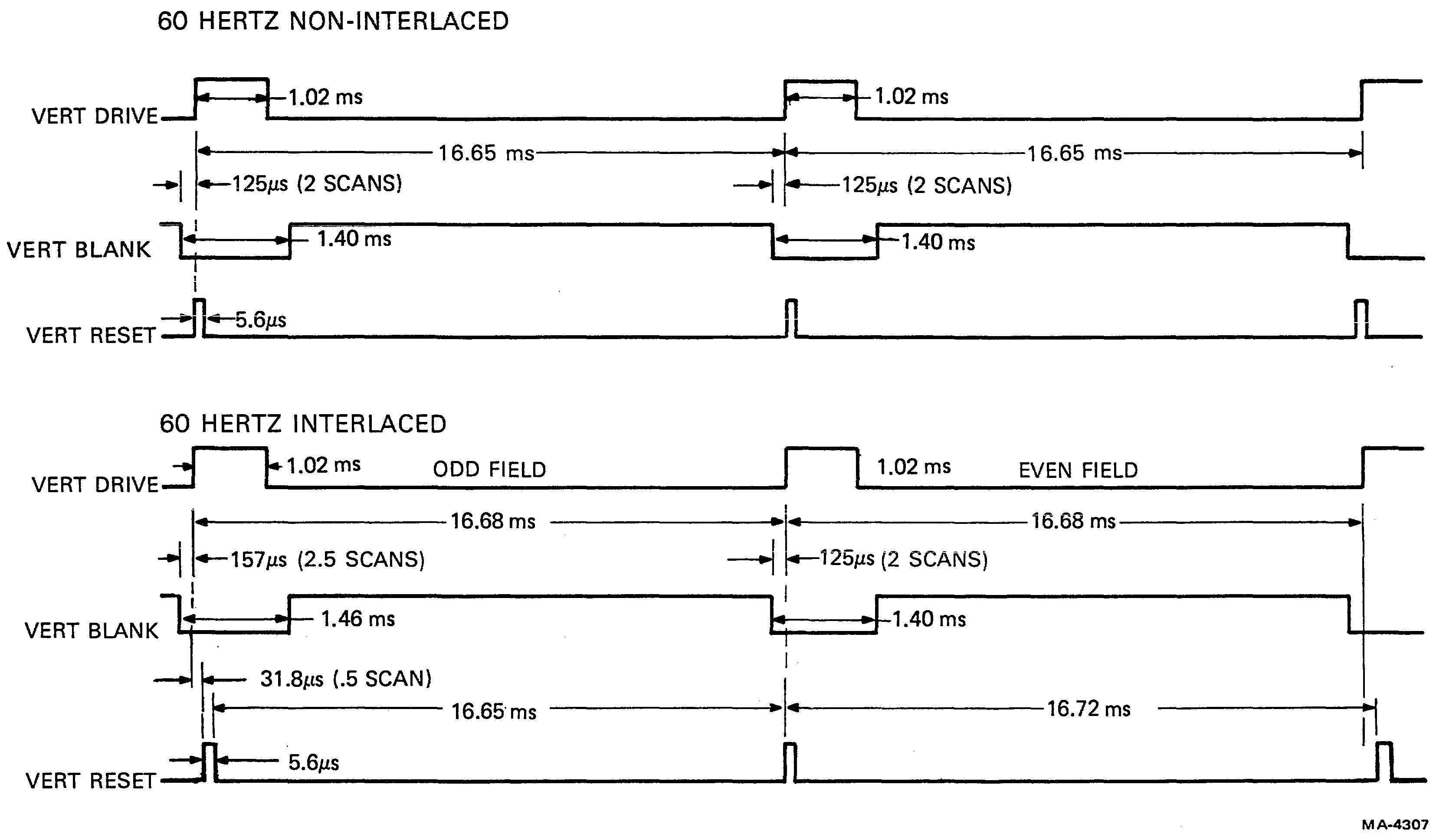

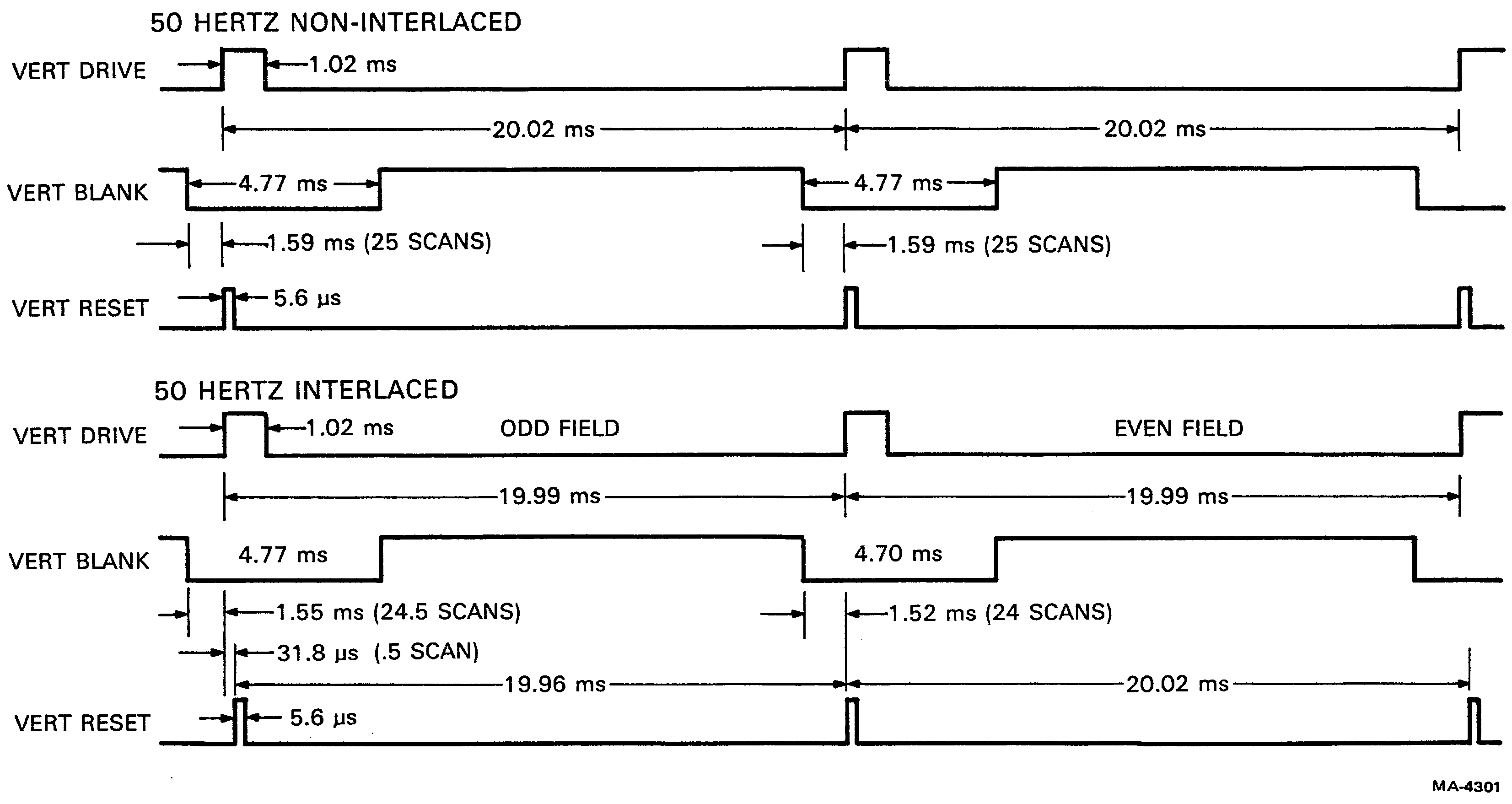

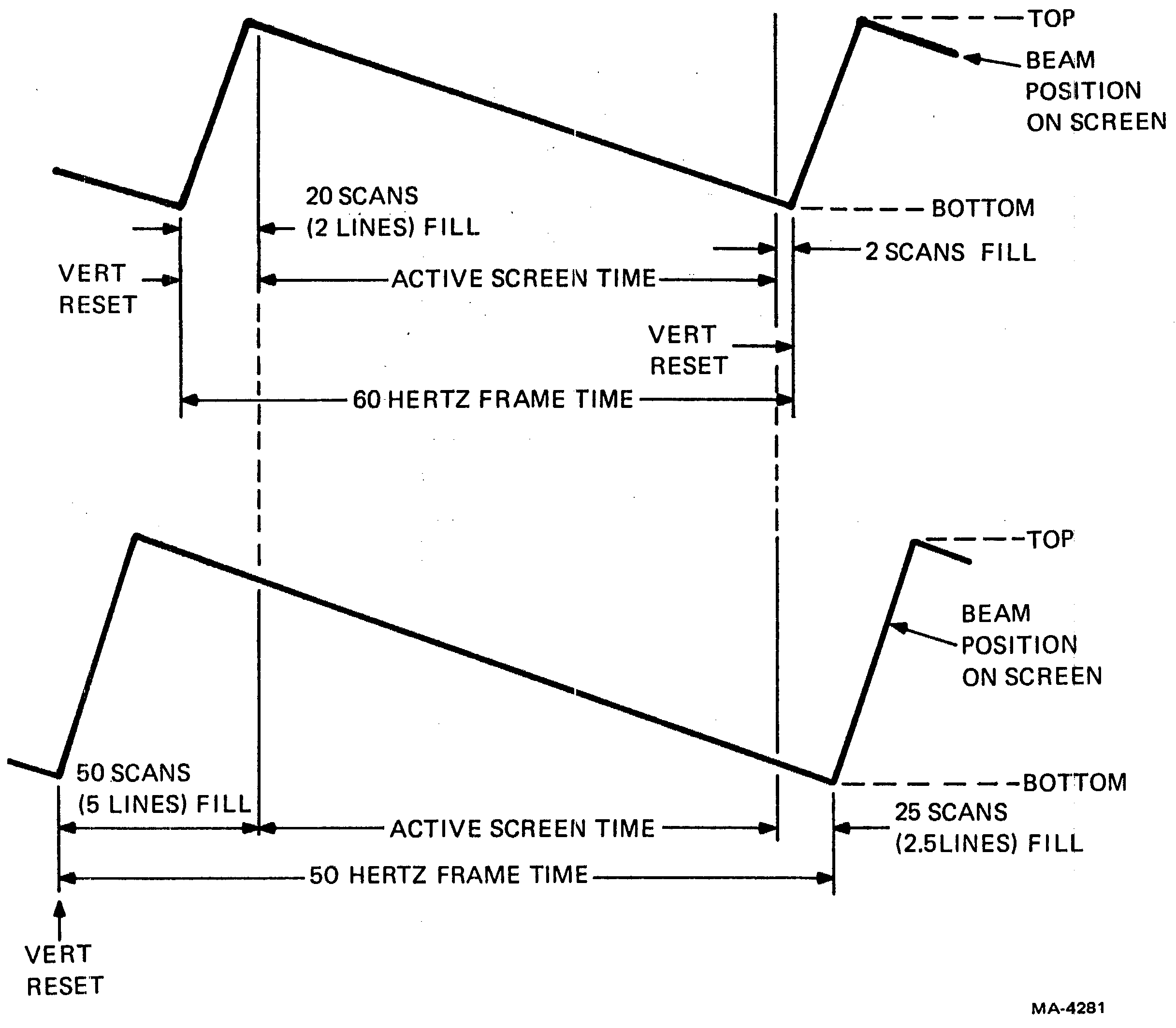

The screen does not hold its image after the electron beam has painted dots on it. For the eye to perceive it as continuously illuminated (i.e., without flickering) the screen must be repainted (refreshed) repeatedly some 30 or more times per second. Also, stray magnetic fields and electrical noise at the power line frequency can cause distortions in the display. If the refresh frequency is different from the power line frequency, the distortions appear to move up or down the display. This is very noticeable. Most distortions disappear by matching the refresh rate to the power line frequency. The VT100 can refresh at either of the two world power frequencies, 50 or 60 Hz, satisfying both flicker and distortion requirements. (VT100 refresh is not locked to the power line but is close enough to conceal most distortions.)

The CRT monitor, the monitor circuit board, and the flyback transformer are replaceable subunits of the VT100.

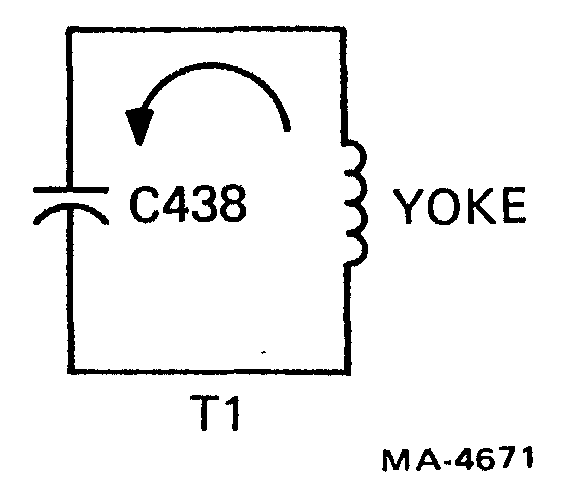

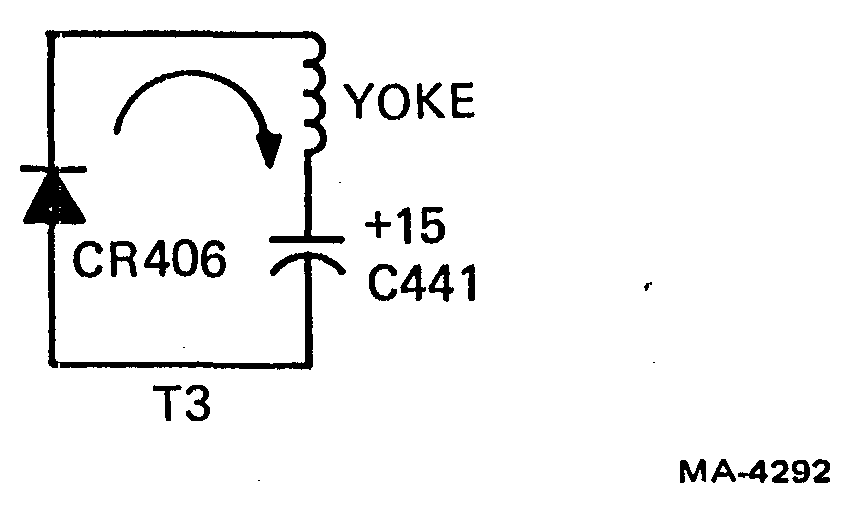

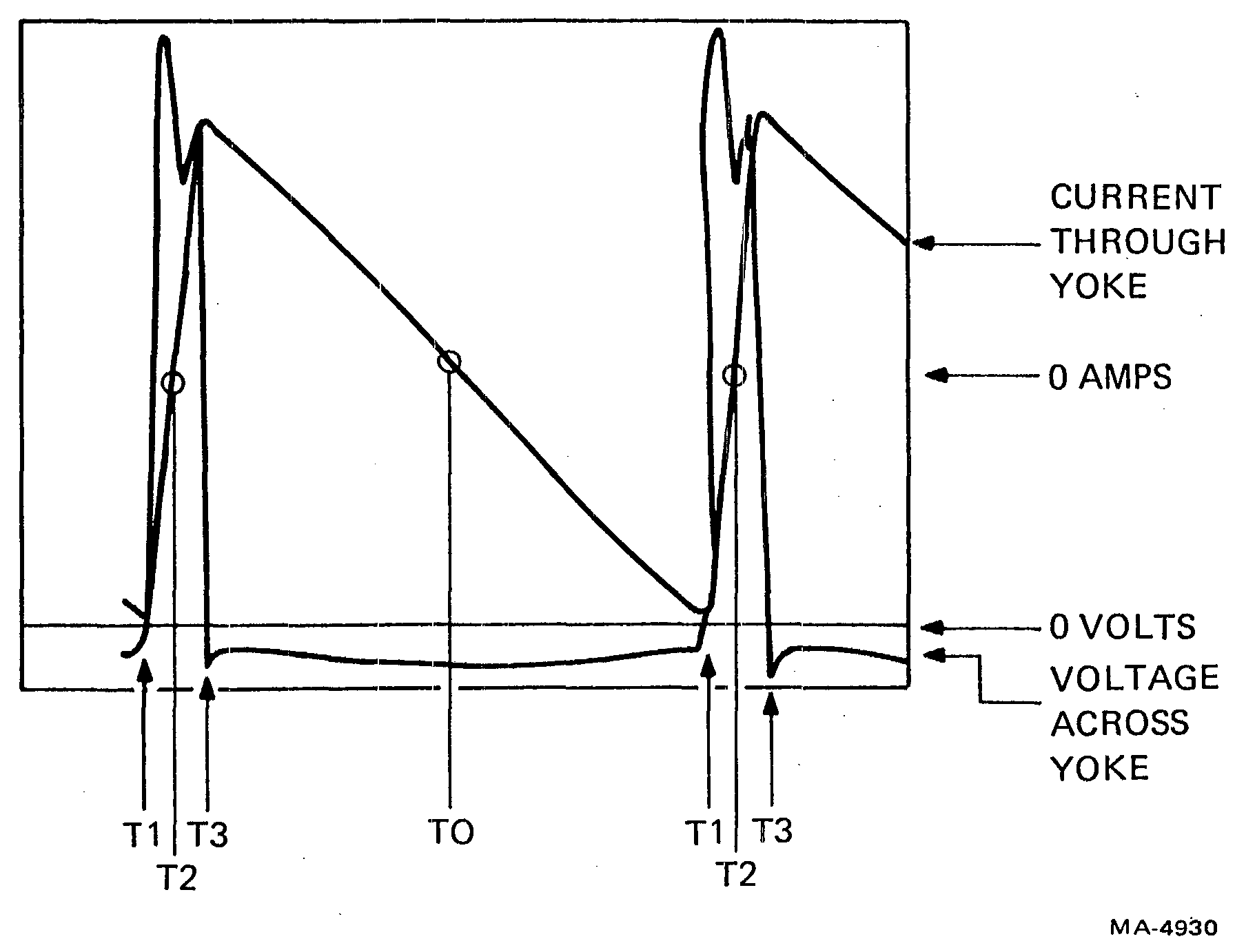

The VT100 power supply provides enough power to run the terminal and a few options. It is a switching supply to allow highest efficiency and to minimize the heat load on the rest of the terminal. It rectifies line voltage directly (without a transformer), and chops the resulting high dc voltage with a transistor at about 30 kilohertz. This ultrasonic ac is stepped down in a relatively tiny transformer and then regulated at low voltage to give the various outputs.

The power supply is a replaceable subunit of the VT100.

The standard terminal port (STP) is a shorting connector in series with the communication port, the modem control lines, and some power and timing lines. By connecting to the terminal through this port, options can exchange signals with the terminal controller or intercept terminal-host communications from inside the terminal cabinet.

The Electronic Industries Association (EIA) interface used on the VT100 is the RS-232-C unbalanced bipolar voltage standard. The terminal controller has two types of ICs that provide conversion between EIA levels and the TTL levels used on the controller board. One IC is a line driver that outputs EIA levels for TTL inputs, and the other senses the EIA levels on the input line and converts them to TTL.

The current loop adapter option plugs into the terminal controller board and mates with the EIA voltage interfaces to convert the terminal to 20 milliampere current loop interfaces. The current loop interfaces can be individually selected to be active or passive.

The 20 mA adapter is a replaceable subunit of the VT100.

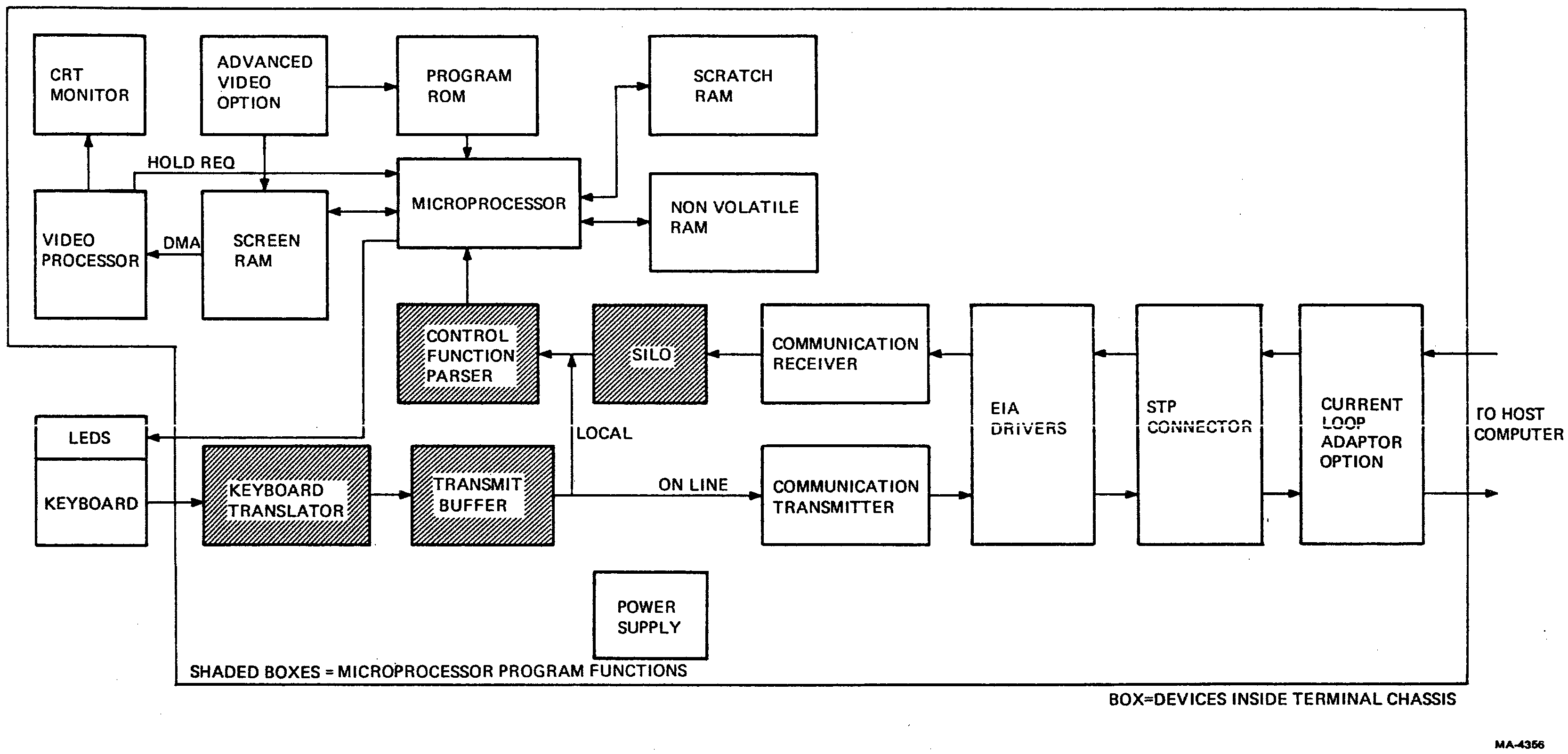

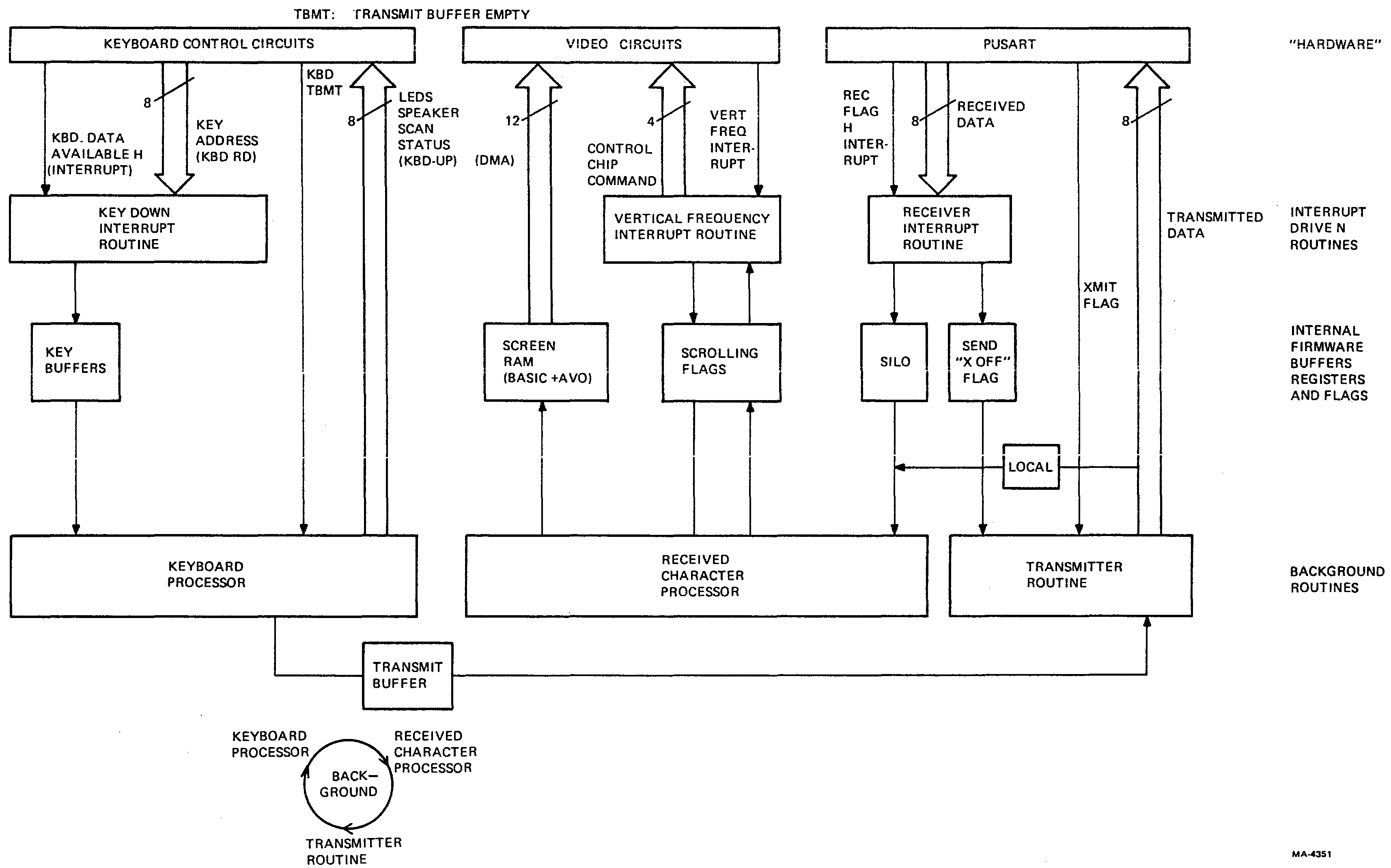

Figure 4-1-3 portrays the VT100 as a system with four levels of operation.

At the deepest level, the background routines continually repeat to manage functions that do not require precisely timed responses. The keyboard processor commands the keyboard to perform address scans, controls the bell and LEDs, and manages the conversion of key information from hardware-dependent codes to ASCII. The transmitter routine manages the transmission of ASCII data to the host. The received character processor examines incoming data, manages the SILO, initiates special functions as specified in the data, and writes displayable data into the screen RAM. When the terminal is in local mode, a logical shortcut bypasses the communication process and allows the keyboard data to enter the received character processor directly.

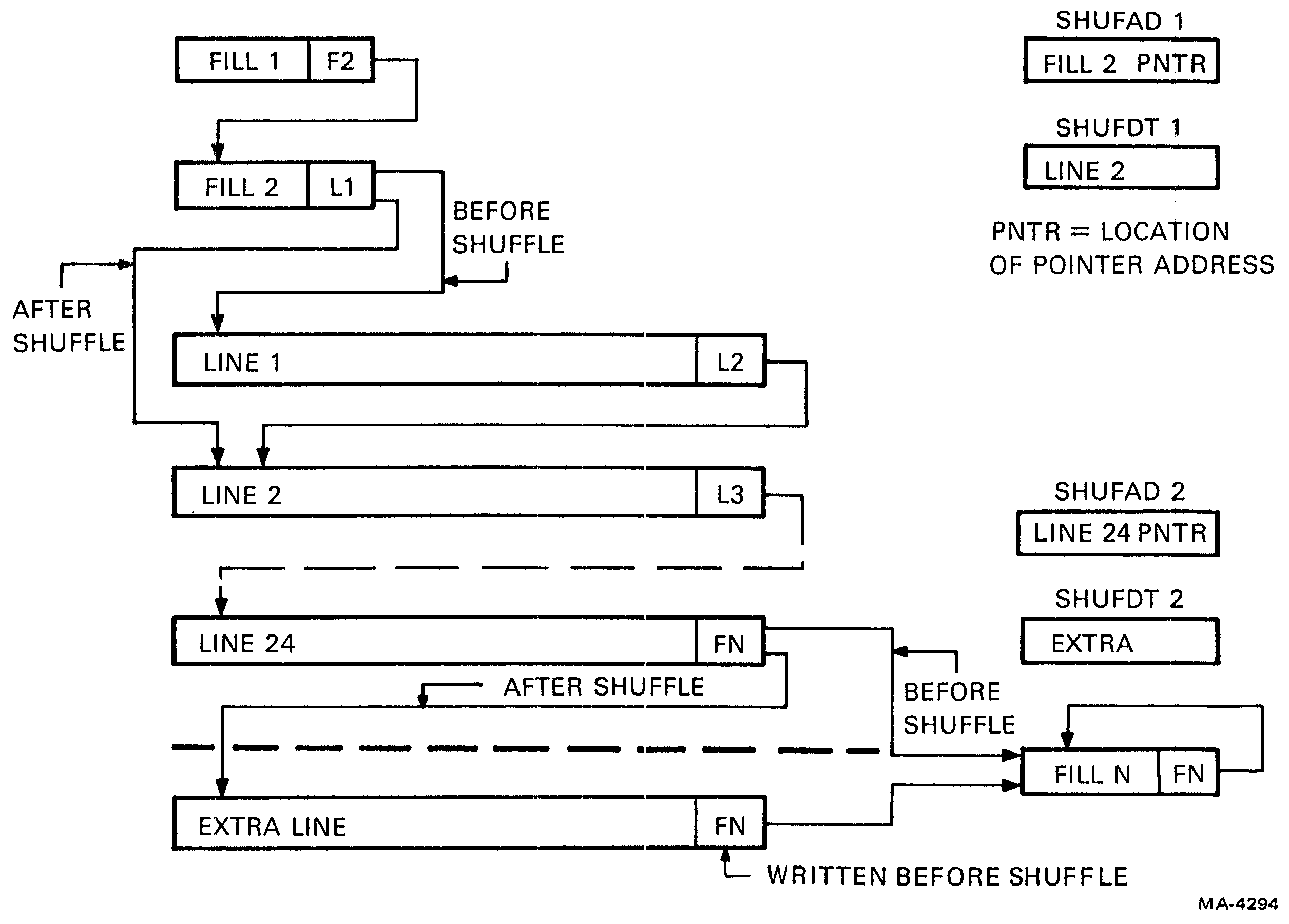

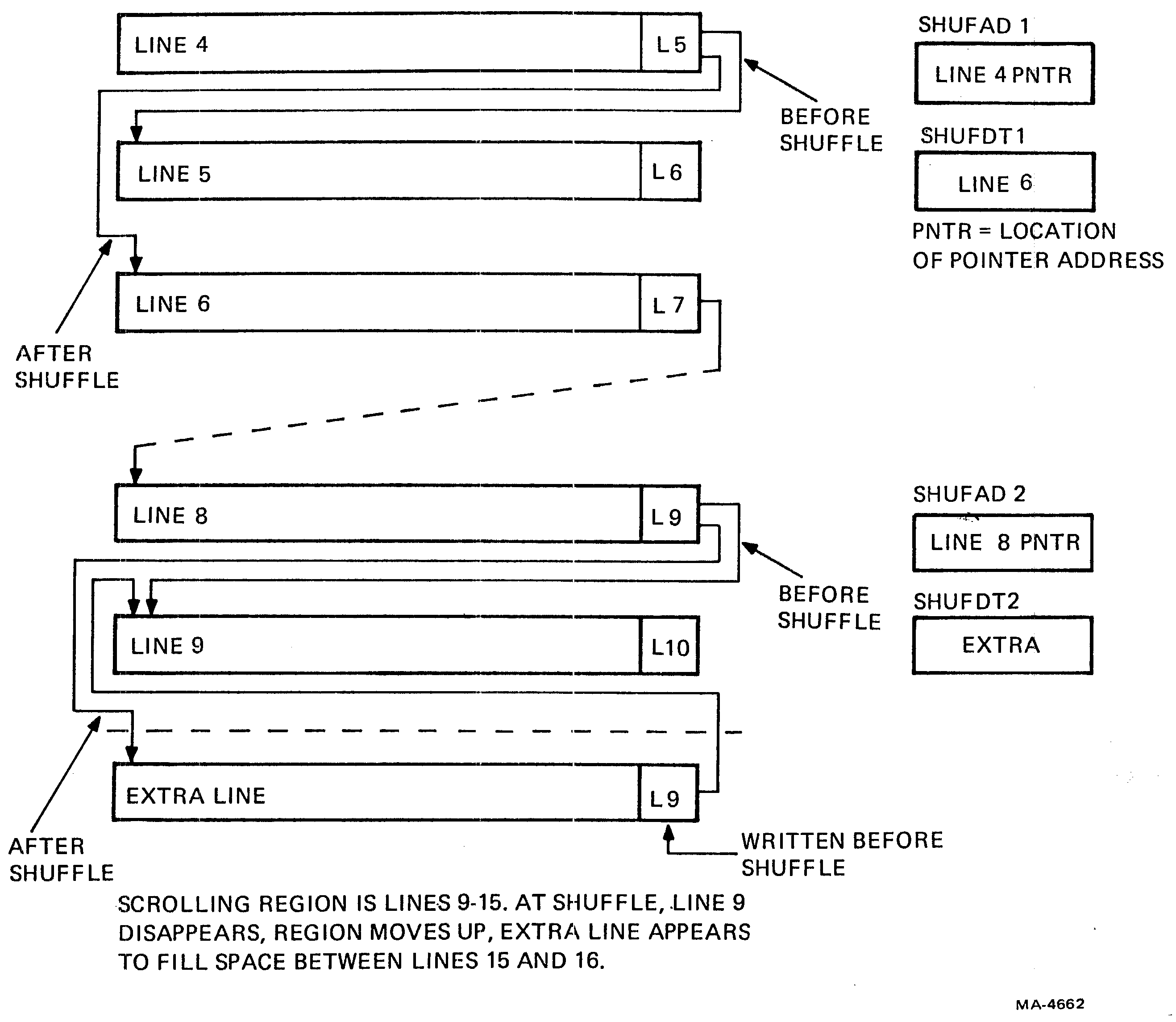

The background routines work on the internal buffers, registers, and flags which are logical devices located in hardware and RAM. These are physical locations in hardware that contain information placed there by the hardware and by the firmware. The key buffers store up to three key addresses for the keyboard processor to pass through the transmit buffer to the transmitter routine for transmission to the host. The screen RAM, which stores the displayable data, is the largest segment of RAM. The scrolling flags contain data for the scrolling process in the video processor. The SILO stores data coming from the host in case the received character processor cannot transfer data to the screen RAM as fast as it arrives. The Send XOFF flag, set by the SILO manager, signals the transmitter routine to send the XOFF code to the host to halt transmission and prevent SILO overflow.

Interrupt routines are segments of the firmware that take precedence over other business in the microprocessor because of the short-lived nature of the data that they handle. The Key Down interrupt routine is initiated by the appearance of data at the keyboard control circuits. It instructs the microprocessor to get the key address from the keyboard UART and put it in the key buffer. The Vertical Frequency interrupt routine occurs every 50th or 60th of a second and provides synchronization of video routines with the actual display timing. The Receiver interrupt routine moves incoming data from the communication transceiver to the SILO.

At the exterior level of the VT100 system, the hardware responds to the firmware by exchanging data between the user and the host computer in forms that are understandable to each.

The VT100 has an 8080 microprocessor at the heart of its intelligence. The 8080 performs all the usual functions of a stored program computer, fetching instructions and data from ROM and RAM and responding to service requests from various devices in the system. Because of technical limitations in the implementation of the microprocessor hardware, some high speed counting and timing circuits and some power circuits are located in peripheral ICs made with a different semiconductor technology. These components are bipolar (8224, 8228) while the 8080 is NMOS.

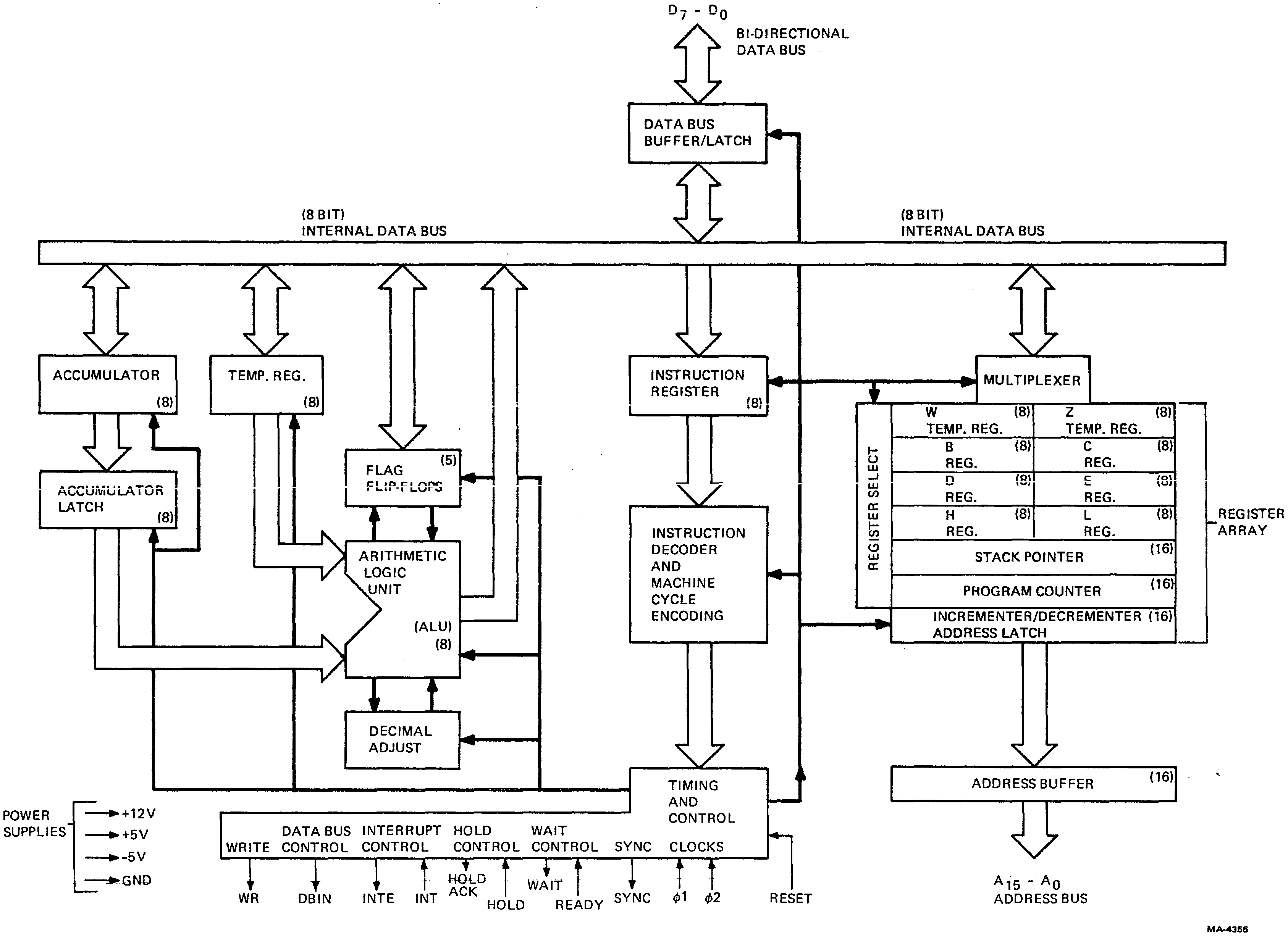

The 8080 (Figure 4-2-1) contains a set of general and special purpose registers (the register array), timing and control logic which responds to machine code instructions, and an accumulator and arithmetic logic unit that perform the computations associated with the microprocessor operation.

The stack pointer is an important register that points to the bottom of the stack. The stack is a last-in/first-out area in RAM that stores information about the current process when a subroutine or interrupt branches away from the current instruction sequence. By storing this information at the beginning of an interruption and restoring it at the end of the interruption, the 8080 can continue the main program without any disturbance. This is the meaning of the interrupt process as it applies to the interrupt-driven routines mentioned in the firmware block diagram in Figure 4-1-3.

Most of the pins on the 8080 are tristate data and address lines. Four pins are power supplies and ground. The others, briefly, are:

For more detail, see Intel’s 8080A manual.

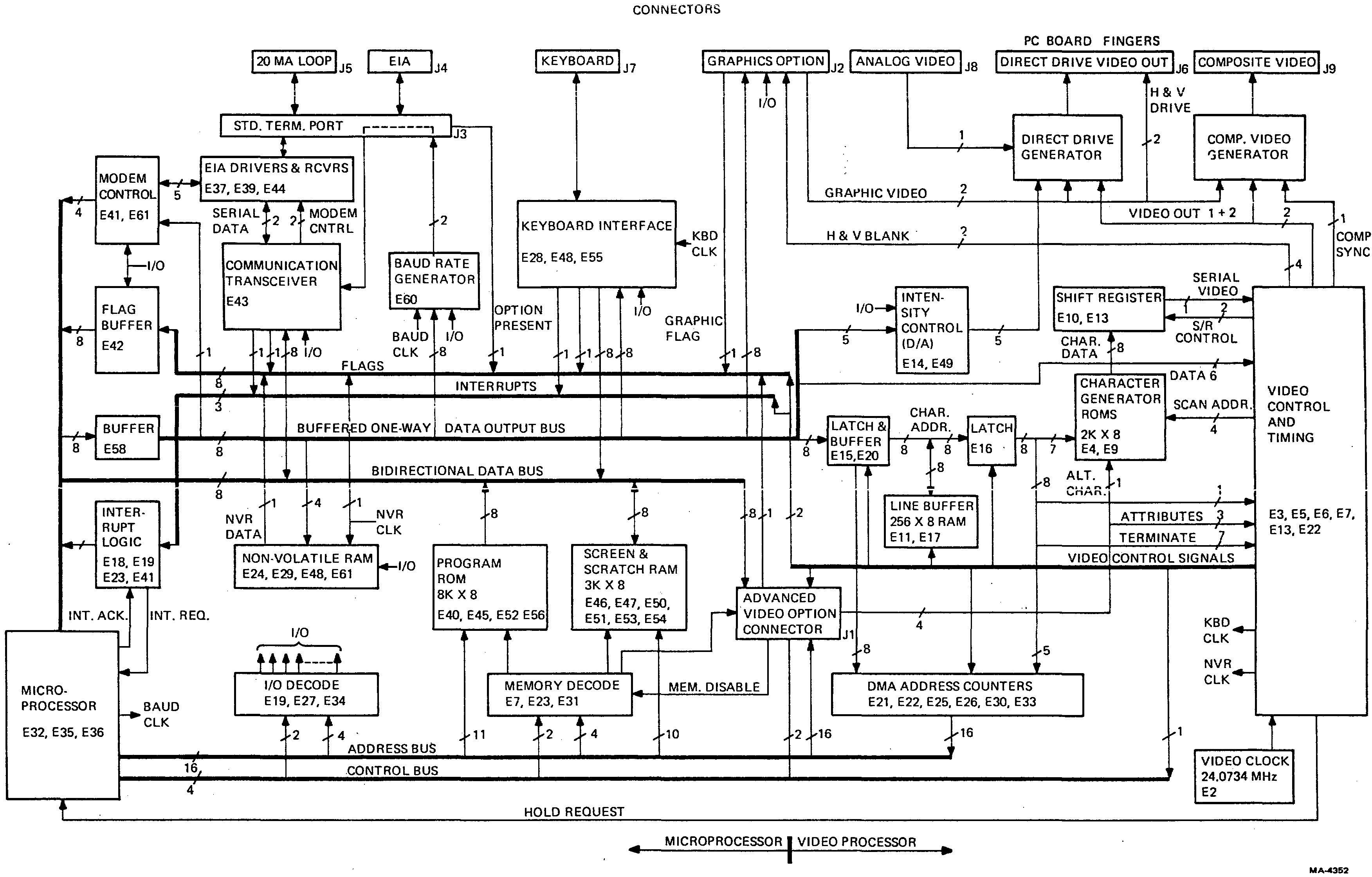

The microprocessor data bus passes directly to the 8228 bus driver and system controller. This device provides TTL output buffering and level translation for the MOS 8080 bus. Because of the large number of devices on the data bus, the drive capability of some devices would be exceeded at times if all devices were on the same bus. (The keyboard UART is the weakest low-level current driver.) To distribute the load, the bus is split into those devices that communicate bidirectionally or are only read by the microprocessor, and those that are only written into. Read and writable devices are on the bidirectional data bus (DB). The write-only devices are driven by a one-way bus buffer and are on the data output (DO) bus. The terminal controller block diagram (Figure 4-2-2) shows which devices are on each bus.

The ROMs do not have sufficient high-level current capacity to drive all of the other inputs on the bus. Inactive devices have their outputs tristated but their inputs still draw enough current to accumulate a significant load over the entire bus. Pull-up resistors are connected to the bus to provide the additional current required. Their resistance is selected to supply enough current to meet high level needs on the bus without exceeding the low level sink capacity of any driving device.

Pull-up resistors are used on the output-only DO bus because the baud rate generator, a MOS device, has an input threshold higher than TTL driver E58 is guaranteed to deliver. Pull-up resistors ensure that the data lines rise enough.

An additional function of the 8228 is a combinational logic decode of the 8080 status byte. This byte, output by the 8080 at the beginning of each machine cycle, contains flag bits indicating the nature and function of the cycle. The byte is latched into the 8228 by the Status Strobe (STSTB) signal from the clock generator. In combination with three control output bits from the 8080, the system controller produces Interrupt Acknowledge (INTA) and Memory and Input/Output Read and Write (MEM WR,RD; I/O WR,RD). These signals reduce the external decoding requirements while saving pins on the 8080 package.

When the video processor asserts Hold Request during a direct memory access (DMA) of the screen RAM, the 8228 floats its outputs. Since these include the memory control signals, the video processor must provide its own memory control. The DMA Enable signal, buffered into the MEM RD line by gate E28 (pin 13), provides memory read enabling during the DMA. The other control signals are pulled high by the pull-up resistors.

The 8224 provides the asymmetrical two-phase clock required by the 8080 logic. Its running frequency is crystal-controlled. An LC circuit on the tank input improves the crystal’s mode stability. The capacitor in series with the crystal compensates for internal phase shifts in the 8224 at the high operating frequency. The 24.8832 MHz crystal frequency gets divided by 9 to produce a 361.69 ns clock period. The buffered TTL phase 2 output clocks the PUSART and the baud rate generator. 361.69 ns is the system clock period for the microprocessor.

The sync signal from the 8080 combines with an internal clock phase to produce the Status Strobe (STSTB) during the last ninth of the first state of each machine cycle. STSTB latches the status byte into the 8228 system controller.

The Ready input is not used in the VT100. It is an asynchronous input that gets synchronized to the machine cycles in the 8224. The synchronized signal can cause the microprocessor to enter a wait state during a memory access to wait for slow memory to respond. Memory used in the VT100 matches the processor speed so Ready is not used.

The Reset input is a Schmitt trigger. Its input is the +5 volt supply delayed by an RC circuit with a diode bypass for fast discharge. The Reset input is held low until well after all power supplies have settled. When the capacitor voltage reaches the Schmitt threshold, reset is released and the microprocessor begins operation at memory location 0 (the start of the firmware ROM). The inverted and noninverted reset signals clear other portions of the terminal controller.

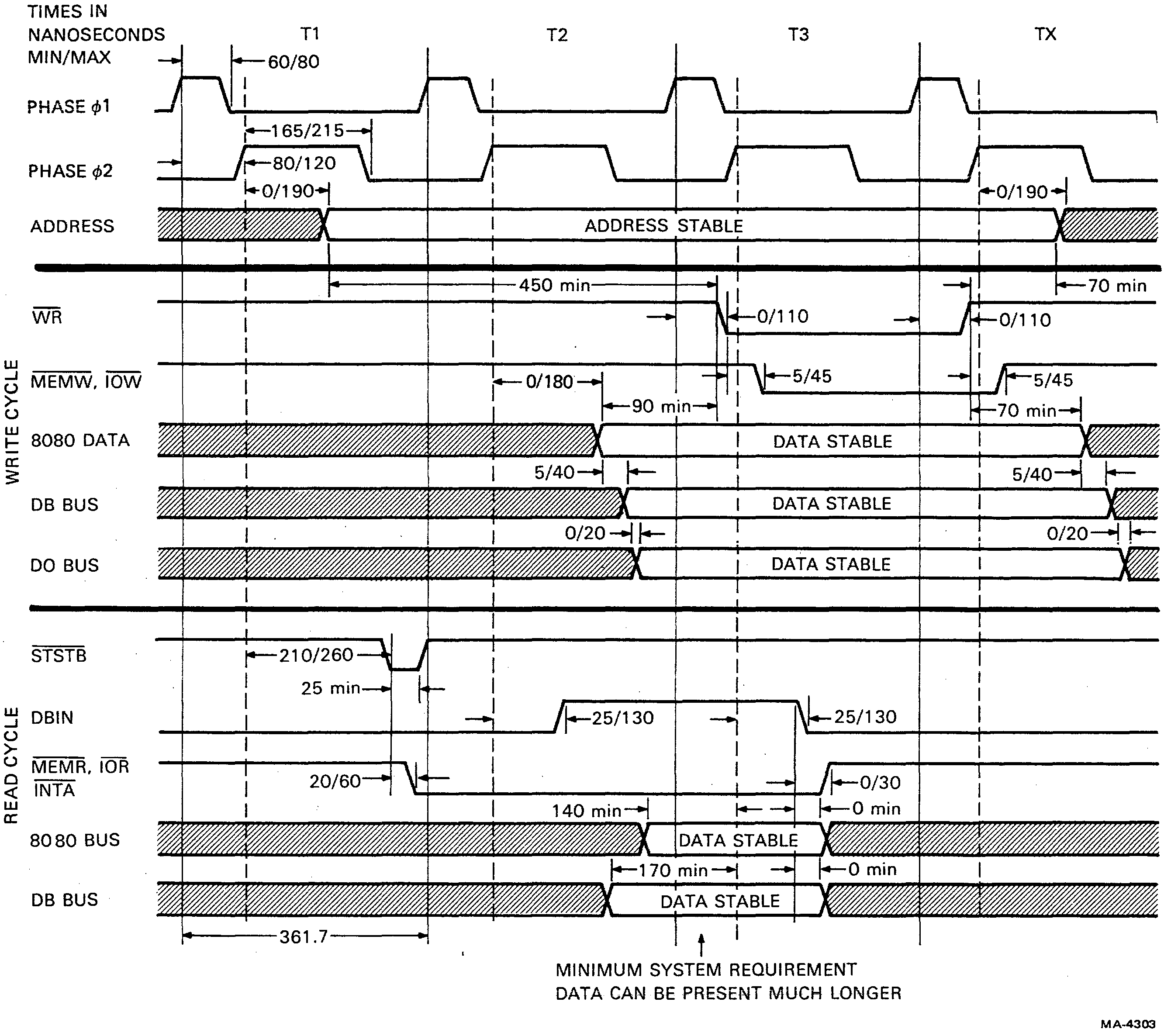

The bus timing diagram in Figure 4-2-3 illustrates the basic time relations between the address, data, and control lines in the microprocessor system. The figure distinguishes between write and read cycles, with the exception of the three top lines. These show the constants of the system: the two clock phases from which all timing is derived, and the address bus, that always provides the current address for either kind of cycle early in the cycle. Numbers on the diagram represent specified minimum/maximum nanoseconds between signals for normal operation.

Starting with the write cycle, note that the status strobe signal (STSTB L) shown in the read section occurs at the same point in the write cycle. Therefore, the status strobe latches the status byte into the 8228 during the first clock cycle. The 8228 delivers the decoded Memory Write L or I/O Write L (MEMW or IOW) signals in the third clock cycle when data to be written is stable. The 8080 Data Bus, DB Bus, and DO Bus graphs show the propagation delays between the three buses. The 8080 bus is the output pins on the chip. The DB bus is the output of the buffered 8228 bidirectional bus, and the DO bus is the unidirectional buffered output-only bus.

In the read cycle, the Memory Read L signal (along with I/O Read L and Interrupt Acknowledge L: MEMR, IOR, INTA) starts early to enable the chip selects and allow the data buses to stabilize. Data Bus In (DBIN) goes high before data settles but does not latch data into the 8080 until its falling edge, when data is settled. The two bus graphs show the assertion of stable data and also show the delay through the bidirectional bus buffer to the 8080 data bus.

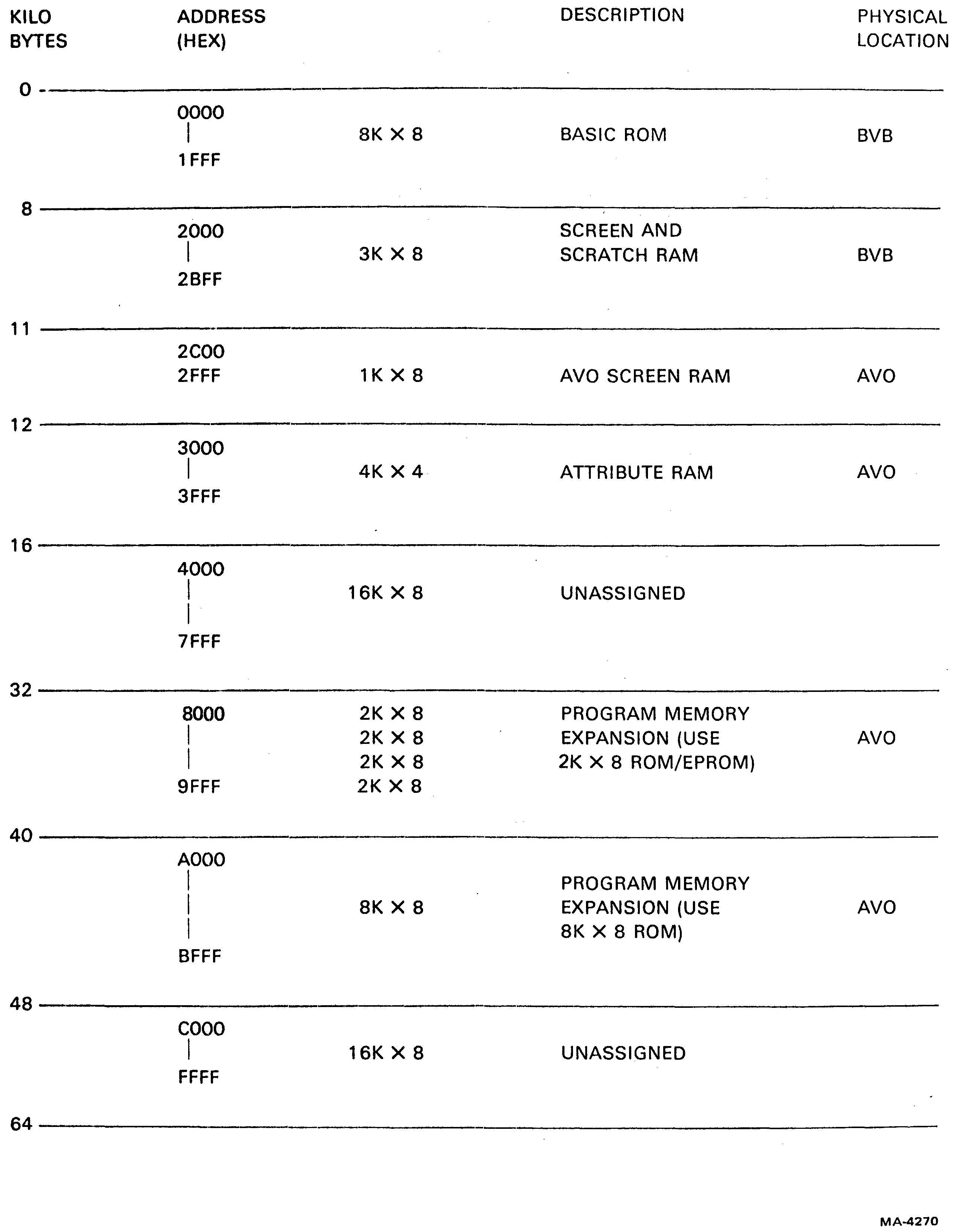

The basic terminal controller contains 8192 bytes (8K) of program ROM and 3072 bytes (3K) of static RAM. (One byte = eight bits.) The original board utilizes four 2K × 8 ROM ICs; later versions may use a single 8K × 8 ROM. The RAM is six 1K × 4 ICs arranged in pairs. The microprocessor can address up to 64K memory locations. Some of these locations are reserved for future expansion. The memory map of Figure 4-2-4 shows the portions of addressable space that are reserved and also those areas that are available for new applications.

The basic terminal controller board contains 8K of program ROM and 3K of screen and scratch RAM. These account for the locations from 0000H to 2BFFH in memory. The advanced video option adds another 1 kilobyte of RAM (2C00H to 2FFFH) to increase the number of characters that can be displayed. The AVO also contains additional memory for character attributes. This memory is only 4 bits wide, but to address each location in correspondence with each of the 4K characters, it uses another 4K of addresses from 3000H to 3FFFH.

The next 16K locations (4000H to 7FFFH) are unassigned. However, 4000H to 4FFFH can be addressed by the video processor using the DMA address counters so 4000H to 4FFFH could be used for additional screen RAM with 5000H to 5FFFH as associated attribute storage.

Above 7FFFH is an 8K area intended for additions or changes to the program ROM in 2K segments and above that is an area intended for the same purpose but in one 8K segment. The top 16K are unassigned.

Each ROM has three ANDed chip select inputs that are mask-programmed to be either active-high or active-low, eliminating the need for external inverters. The programming provides 1 of 4 decoding of the two address lines A11 and A12. The third chip select line is common to all four ROMs. In later VT100s jumpers W2 and W3 can be used to select either a high or low assertion for this single chip select to allow for 64K ROMs that do not have a programmable chip select. Table 4-2-1 shows the addressing of the ROMs.

| Address Line 11 | Address Line 12 | Chip Select 2 | Chip Select 3 | ROM Selected |

|---|---|---|---|---|

| 0 | 0 | Active Low | Active Low | 1 |

| 1 | 0 | Active High | Active Low | 2 |

| 0 | 1 | Active Low | Active High | 3 |

| 1 | 1 | Active High | Active High | 4 |

The program ROM is enabled when the top half of memory decoder E31 is enabled and the correct address space is requested by the microprocessor. MEM RD or MEM WR from the 8228, in the absence of MEM DISABLE, enables the decoder. The ROM is in addresses 0H to 1FFFH, so A13 (the 8K bit) is not asserted during ROM reads. Bit A12 is low or high for 0-4K or 4-8K sections of ROM. The decoded outputs from both states are ORed to provide one of the select signals for the ROM. Then bits A11 and A12 at two of the chip select lines enable the outputs in one of the 2K segments. The low 11 bits address one of the 2K bytes in the enabled ROM. If the program is in one 8K ROM, A11 and A12 are used as regular address lines; only one chip select line enables its outputs.

If A13 is asserted, the memory space between 2000H and 3FFFH is being addressed. The ROM outputs are disabled and the decoded output from the top half of the decoder enables the bottom half. Now bits A10 and A11 are decoded to select 1K segments of the screen RAM. The 1K × 4 RAMs are paralleled in pairs to make each location 8 bits wide. There is 3K on the basic video board. The fourth 1K is located on the AVO; its addressing is decoded separately.

Memory Disable turns off all memory on the terminal controller board. It is used by options that plug into the advanced video option connector:

The advanced video option can contain overlaying program memory. This is a set of address locations that the AVO can be jumper-programmed to decode and provide data for. Since the main memory may also be decoding the same location, the AVO must assert MEM DISABLE to disable the main memory (ROM and RAM) so that only one data byte is asserted on the bus.

The I/O address space is divided into two regions: one, containing the 8251 PUSART, has address bit A01 always low; the other region contains all other I/O devices and has bit A01 always high. The list of I/O addresses in Table 4-2-2 illustrates this by the presence of hex 2 in the low half of each non-PUSART address byte.

| READ OR WRITE | |

| 00H | PUSART data bus |

| 01H | PUSART command port |

| WRITE ONLY (Decoded with I/O WR L) | |

| 02H | Baud rate generator |

| 42H | Brightness D/A latch |

| 62H | NVR latch |

| 82H | Keyboard UART data input |

| A2H | Video processor DC012 |

| C2H | Video processor DC011 |

| E2H | Graphics port |

| READ ONLY (Decoded with I/O RD L) | |

| 22H | Modem buffer |

| 42H | Flags buffer |

| 82H | Keyboard UART data output |

When bit A01 is low, the PUSART is enabled. The I/O RD and WR signals from the 8228 control the read or write operation. Address bit A00 selects either the command or data register for the I/O operation.

When bit A01 is high, the PUSART is disabled. Bit A01 high is one of two signals required to enable the I/O write decoder (E27). I/O WR is the other signal. Address bits A05, A06, and A07 select one of the seven writable I/O devices. These are the baud rate generator, the brightness control D/A latch, the NVR latch, the keyboard UART transmit buffer, the DC011 and DC012 video processor chips, and the graphics processor data port.

Only three I/O devices are readable so their addresses were chosen to allow read decoding directly from the three address lines. When the 8228 asserts I/O RD, I/O WR deasserts and decoder E27 is disabled. I/O RD enables the gates in E34 to allow reading of the keyboard UART receive buffer, the flag buffer, or the modem control signal buffer, depending on which address bit is asserted.

When any of the three interrupting devices (communication receiver, vertical frequency, or keyboard) sets Interrupt Request (INTR H) through gate E23, the current instruction is completed and then the microprocessor sets its Interrupt Acknowledge (INTA) status bit and performs an instruction fetch. The address requested in the fetch is the contents of the program counter. Its value is ignored in the interrupt process, but it is not incremented, as it would be in a normal fetch cycle. The INTA bit is decoded from the status word in the 8228 system controller; it enables the tristate interrupt vector buffer (E41) which then presents a restart (RST) instruction to the data bus. Main memory does not conflict with the vector buffer because the 8228, in decoding the interrupt status word, does not produce the memory read or write command bits needed for address decoding. (Refer to Table 4-2-3.)

| 00H | Power-up (Not hardware driven) |

| 08H | Keyboard |

| 10H | Receiver |

| 18H | Receiver and keyboard |

| 20H | Vertical frequency |

| 28H | Vertical frequency and keyboard |

| 30H | Vertical frequency and receiver |

| 38H | Vertical frequency, receiver and keyboard |

The RST instruction disables further interrupts, pushes the current program counter contents (the location of the next instruction in the interrupted program) onto the stack and decrements the stack pointer. Then the program counter is loaded with the bits in the address field of the RST instruction. This field is produced by the interrupt signals of the interrupting devices. The signals are passed onto the data bus as bits in the address field (bits 3, 4, and 5). The rest of the instruction is hard-wired through diodes that supply high level to the other data bits during INTA and that are reverse-biased to isolate these data bus lines when the vector buffer is inactive.

The RST address field, when mapped into the same bit locations in the program counter, defines a set of eight 8-byte long memory spaces at the beginning of the memory. The first address, 0, is the starting point for the terminal controller program and is not used for interrupts. The program is normally started by a hardware reset signal that sets the program counter to 0. It can also be started by an escape sequence that the host can send to force the program to jump to zero, or in SET-UP mode the RESET key can be pressed. The other seven memory spaces, starting at 8, 16, etc., contain jumps to places in an interrupt handling routine that can mediate requests for service from any of the seven combinations of interrupting devices.

At the end of the interrupt service routine, the stack is popped, interrupts are enabled, and the interrupted program continues.

Early VT100s can disable the receiver interrupt by programming D4 in the NVR latch. However, this is never used by the VT100. Later VT100s instead, have the ability to add a Communications Transmit Buffer Empty interrupt by adding W6. The 8080 would then have to distinguish transmit and receive interrupts by testing the transmit flag on the flag buffer. This provision is not used on the VT100.

When power is first applied to the terminal controller board, the reset circuit in the 8224 holds the microprocessor in a halt state. Within a second, after the voltages stabilize in the power supply, the RC network at the reset input allows the input voltage to rise to the switching threshold of a Schmitt trigger. Then the reset is released with the 8080 program counter set to 0. The low 64 bytes of program are reserved for the eight interrupt service routines which can be addressed by the restart instruction (see previous section). The low 8 bytes start the power-up routine by disabling the interrupts, setting up the stack pointer, and then going immediately into the self-test routines.

Assuming there are no hard logic failures present on the board, the microprocessor attempts to perform a confidence check of the controller. Some failures are considered fatal and will stop the machine; other failures limit its operation but will not prevent its use. Fatal failures are indicated by the LEDs on the keyboard, while nonfatal errors are indicated as a single character on the screen.

The microprocessor first sends the number of the first ROM to the LEDs on the keyboard. Then it calculates a checksum of the contents of the first 2K of program. (Since firmware is treated as four 2K blocks of code, later VT100s with one 8K × 8 ROM chip operate the same way but any block failure requires replacement of the one chip.) At the time of ROM preparation, a special byte was included within each block to make the checksum equal zero if there are no errors. If there is an error, the microprocessor halts and the LEDs indicate the current ROM at the time of failure. Otherwise, the LEDs are incremented to show the next ROM number and the process continues.

The next part of the test is writing and reading the RAM. Every bit in the RAM is written with a 0 and a 1 and read each time. If the advanced video option is present (as indicated by the Option Present flag), its RAM is tested immediately after the main RAM. In the main RAM a failure halts the machine. Failure of a bit in the advanced video option RAM is indicated on the screen and the process continues. In another terminal, like the VT52, one bad bit in the screen RAM means there is one location that may not contain the right character. This can be annoying to the user but does not affect the rest of the screen. If one bit is bad in a VT100 line address, the entire screen below the affected line can become garbled and unusable. A bad bit in the scratch area could disable communication with the host. So this confidence check ensures that any RAM failure is detected immediately.

The next test checks the nonvolatile RAM by reading it. A checksum is calculated and compared with the value stored the last time the NVR was written during a save. A bad NVR does not stop the VT100 because the SET-UP values can always be reestablished from the keyboard at power-up. The NVR test is also the normal time when the terminal gets its auto SET-UP readings from the NVR. Time is saved because reading the NVR is the most time-consuming part of both the self-test and the auto SET-UP. If the NVR fails, the bell sounds several times to inform the operator, and then default settings stored in the ROM allow the terminal to work. The operator must then manually reset any parameters that differ from the default values.

To test the keyboard, the microprocessor commands the keyboard to scan once, lights all the LEDs, for about a half second, and sounds the bell. It waits for the scan to finish and then looks for the last key address 7FH at the keyboard UART. If the test fails, the terminal remains on-line, making it a receive-only (RO) terminal.

This is the end of testing.

Once the NVR data is in the scratch area in RAM, the microprocessor uses that data to program the hardware. All operating parameters that were last saved (see NVR) are recalled and the terminal is set to match them. Finally the cursor appears at column 1, line 1, and the microprocessor enters its background routine, ready for operation.

Refer to the Communication chapter for a discussion of Data and EIA tests, and to the Service chapter for a listing of the Self-Test Results tables.

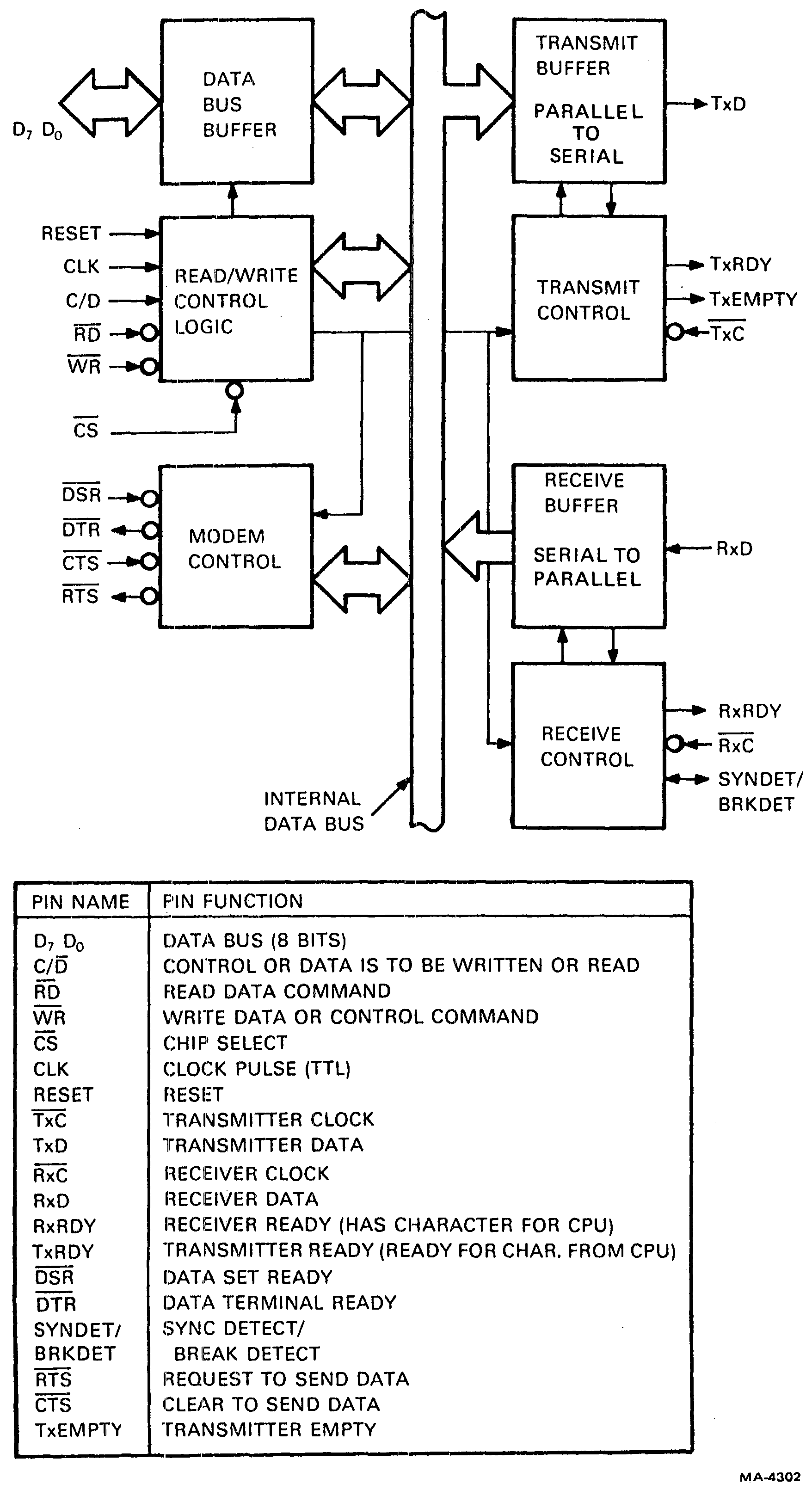

The VT100 interfaces to its host system through a serial data port. An 8251 programmable universal synchronous or asynchronous receiver-transmitter (PUSART), illustrated in Figure 4-3-1, drives the port. This device translates between parallel and serial formats, adding or removing start and stop bits as required. The data exchanged are ASCII characters; parity may be enabled or disabled; the selectably odd or even parity bit will take the most significant bit position.

Most data in computer systems is exchanged as groups of bits. The bit is the smallest unit of information, but to be useful, most information must be encoded into groups of bits in standardized patterns. The VT100 operates with the standard patterns described by the American Standard Code for Information Interchange (ASCII). ASCII defines the use of 7 bits, specifying 128 different patterns that correspond to almost all of the letters, numerals, and punctuation marks used in English and several other languages. An eighth bit is reserved for an expanded standard.

The eight ASCII bits can be exchanged most rapidly over eight separate wires (in parallel), but this is very expensive to do anywhere outside the computer cabinet. Instead; the bits are rearranged to pass over a single wire one after the other. This is called serial transmission. The circuitry for converting parallel to serial and back again is complex but suited to large scale integration (LSI). The savings allowed by the use of serial lines has encouraged the development of very sophisticated but inexpensive conversion devices in LSI. At the same time, a variety of data exchange protocols has been developed. The result is an LSI device that can operate with virtually any protocol depending on the programming that it receives from its local processor. This is the PUSART. The VT100 uses one such device (Intel’s 8251A) only in asynchronous mode, plus two simpler, wire-programmed asynchronous-only UARTS for the keyboard interface.

Synchronous and asynchronous describe the manner in which separate groups of bits (called bytes) are exchanged. In order for a receiver to know which bit is arriving at any given time, it must know the format of the byte and which bit of the byte is the first one. In synchronous mode, one or more special bytes are transmitted which the interface recognizes as synchronizing characters. Then all data bytes are transmitted together in rapid and precisely timed succession. Both the transmitter and receiver must have the same externally-supplied clock.

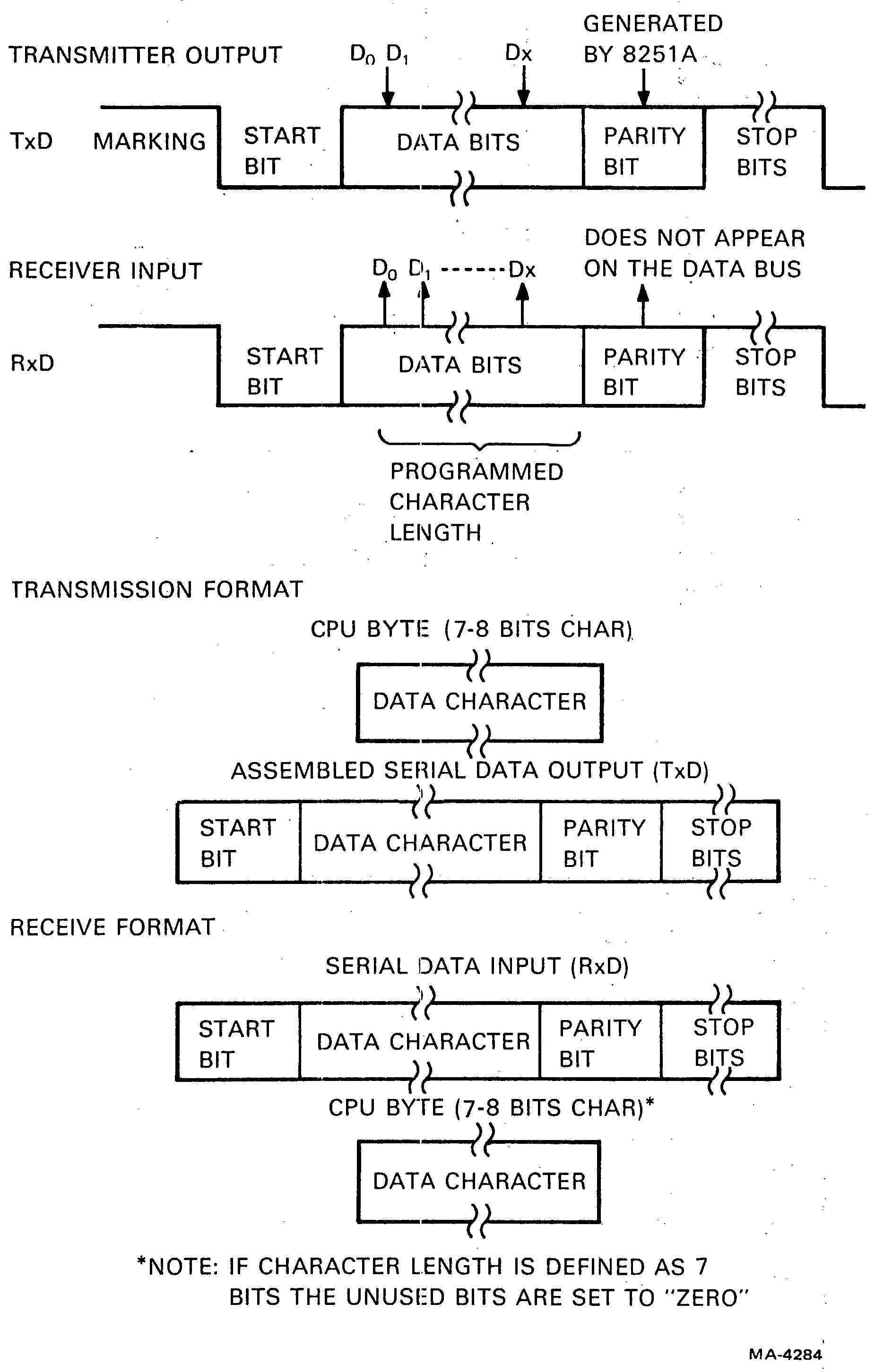

The VT100 only communicates asynchronously. Asynchronous transmission uses bits added to each data byte to provide synchronization between the transmitter and receiver. Because any two data exchanges can originate at random times with clock frequencies as much as 1 percent different, the protocol assumes random arrival of any byte of data, and relies on the synchronization information in the byte. This synchronization consists of extra bits appended to the beginning and end of the byte. One bit at each end (one start bit and one stop bit) is the most common configuration. The start bit and stop bit are defined to have specific states, and in particular, the start bit has a different state from the idling condition on the line. The interface looks for the transition from the idling state (called mark) to the start bit state (called space) and then clocks in the byte. The stop bit is the mark state, as is the idling line, so an immediately following byte has the correct mark to space transition to provide synchronization. The data bits, which occur between a start and a stop bit, are represented by a mark for a one and a space for a zero. Figure 4-3-2 shows the asynchronous data format.

The complete functional definition of the PUSART is programmed by the system’s software. A set of control words must be sent out by the microprocessor to initialize the PUSART to support the desired communications format. Once programmed, the PUSART is ready to perform its communication functions. The Transmitter Ready (TxRDY) output is raised high to signal the microprocessor that the PUSART is ready to receive a data character from the microprocessor. TxRDY is reset automatically when the microprocessor writes a character into the PUSART.

Upon receiving an entire character from the serial input, the Receiver Ready (RxRDY) output is raised high to signal the microprocessor that the PUSART has a complete character ready to be read. RxRDY is reset automatically when the data is read. The PUSART cannot begin transmission until the Transmitter Enable (Tx Enable) bit is set in the command instruction and it has received a Clear To Send (CTS) input. The Transmit Data (TxD) output will be held in the marking state when the line is idle.

For a more detailed description of the PUSART’s operation, refer to Intel’s 8251A specification.

I/O read, write and enable addressing and commands are discussed in the microprocessor I/O decoding section.

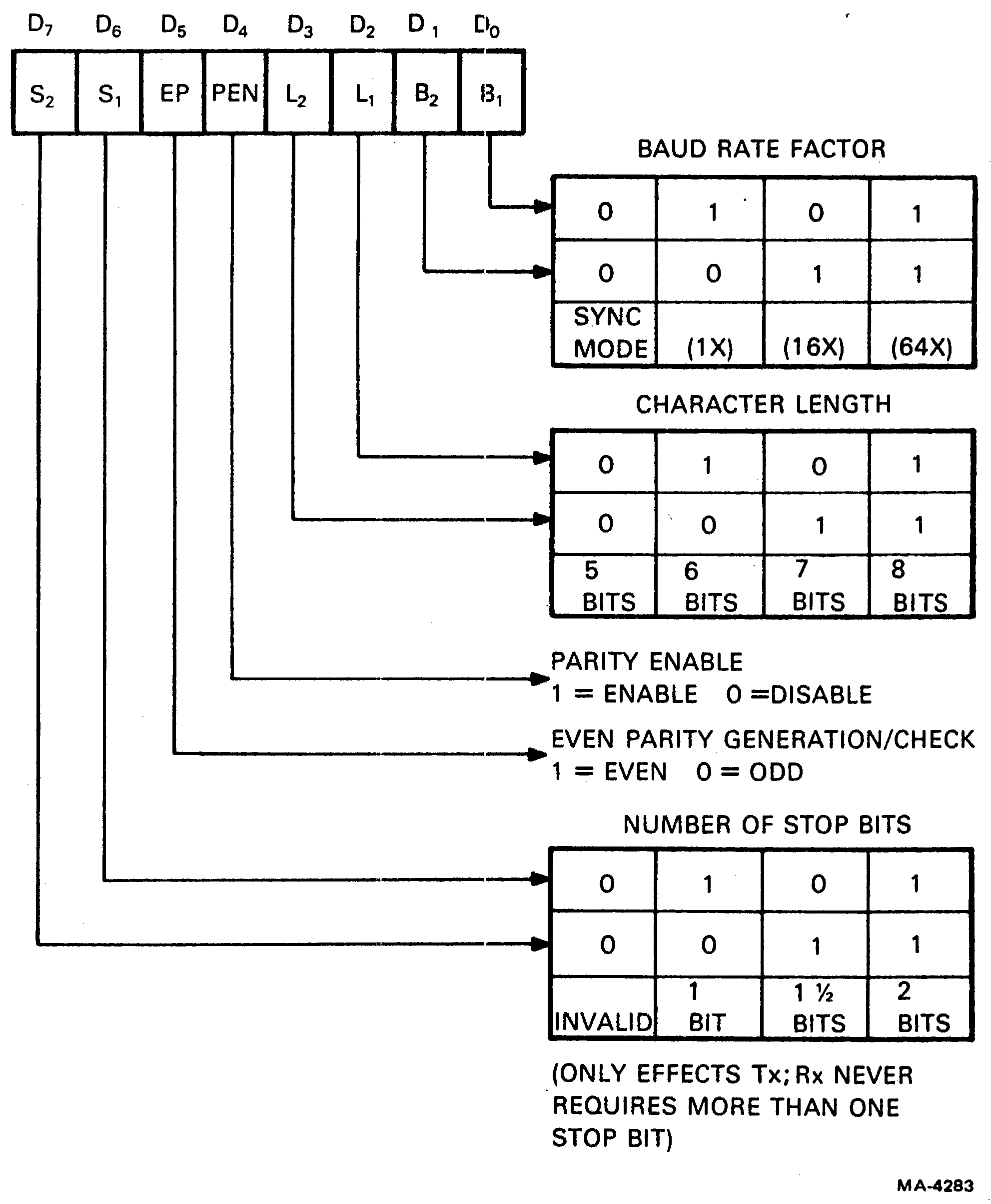

The microprocessor can program the PUSART to operate with several standards and parameters. Many of these parameters are predetermined by the VT100 specifications. Character length, number of stop bits, parity enabling and format, baud rate multiplication factor, and asynchronous operation are all programmed in at power-up through the mode instruction (Figure 4-3-3) from the stored SET-UP information. Address bit A00 selects either the command register in the PUSART for writing the byte containing this information, or the transmit buffer for normal operation. A different programmable device, discussed later, provides the selected baud rate from SET-UP data.

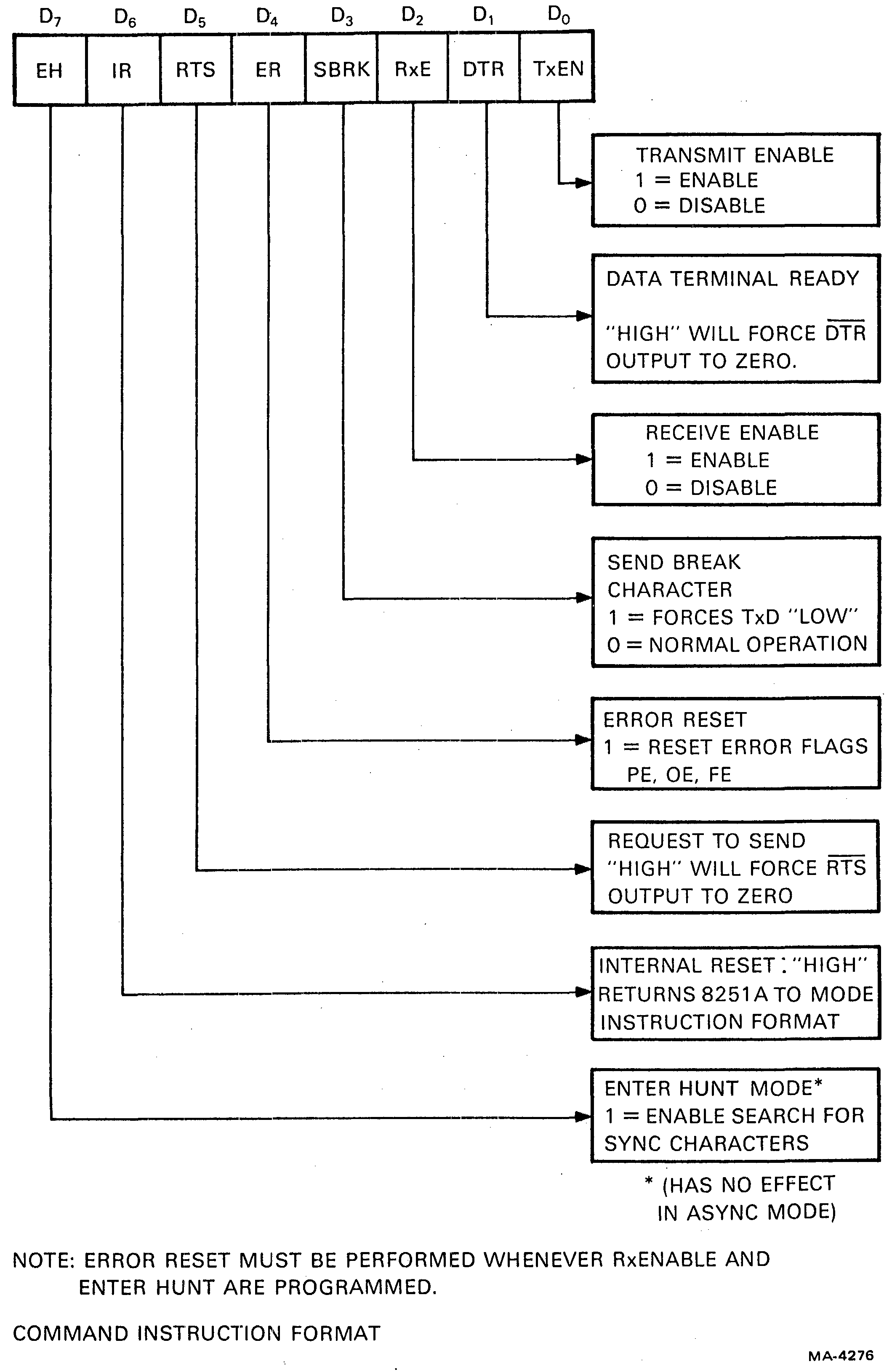

After the PUSART mode of operation is selected by writing a mode instruction, PUSART operation is controlled by writing a command instruction (Figure 4-3-4). Once the mode instruction has been written into the PUSART, all further “control writes” (C/D̅=1) load a command instruction. A reset operation (internal or external) returns the PUSART to the mode instruction format.

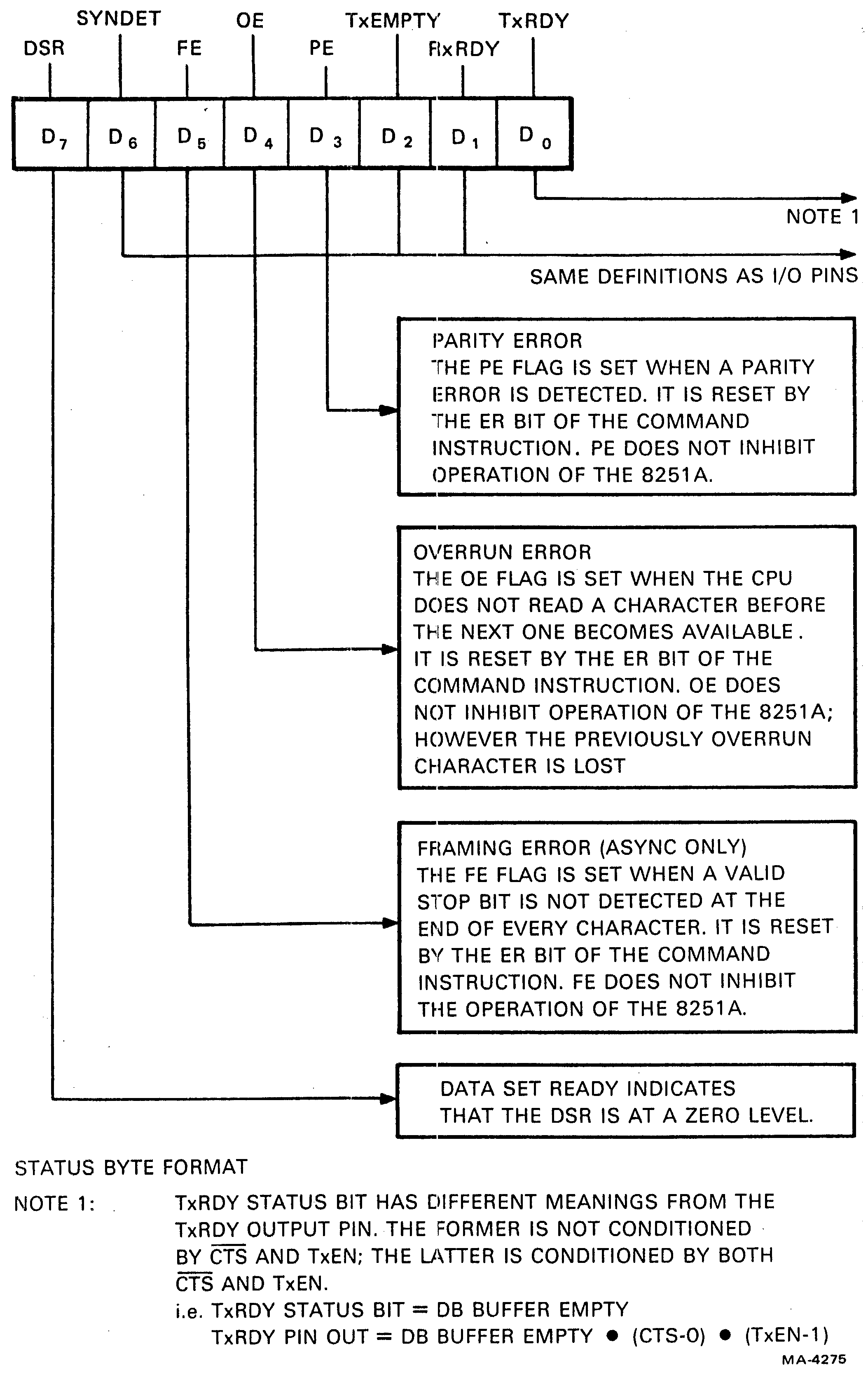

The status of the PUSART can be read by the microprocessor by performing a read with C/D̅=1. Some of the bits in the status word (Figure 4-3-5) have the same meaning as output pins on the PUSART chip. The status word may be a maximum of 28 clock periods behind the event causing the update. This clock, from the microprocessor’s phase 2 TTL signal, is the clock for the internal operation of the PUSART, which is a dynamic device requiring internal refresh at regular intervals.

When the microprocessor wants to send a character out, it checks the XMIT flag at the flag buffer. If this flag is high the transmit buffer is empty and can accept data. If the flag is low, the microprocessor continues through its background program and returns to check again later.

When the flag is high, the microprocessor loads a data byte into the transmit buffer. The PUSART is double-buffered; this means that there is a second data buffer inside that is automatically loaded from the first buffer. The second buffer’s contents get start and stop bits and parity (if enabled) appended and are shifted out by the continuously running clock. Immediately after the second buffer is loaded, the transmit flag goes high and the first (transmit) buffer can be loaded again.

Any data that appears on the receive data line is shifted into the internal receive shifting buffer. When a full character of bits has arrived, the start, stop, and parity bits are stripped. Parity is checked, and if bad, the parity error flag in the status word is set. Data is transferred to the receive data buffer, and the receive flag is set. This flag requests an interrupt from the microprocessor. The microprocessor then has the amount of time it takes the next character to shift in to read the first character. After reading the character, the microprocessor reads the status byte to check the integrity of the data. If the microprocessor does not read the receive data buffer in time, the second character writes over the first one which is lost. Then, an overrun error is reported in the status word. The checkerboard character appears for all errors.

PUSART clocks are derived from the microprocessor clock. The microprocessor clock crystal was selected to provide a frequency within the limits of the 8080 which could be readily divided to provide standard baud rates. The division occurs in programmable baud rate generator E60. This device contains two independent counters to allow different receive and transmit (split) baud rates. Each counter has 4 input lines to select 1 of 16 rates. Thus, a 1-byte load into the device can set up both send and receive rates. The baud rate generator’s input register is written into as a device in the I/O address space.

E60 is factory mask-programmed with the division ratios required to get standard baud rates from the crystal frequency. The 4-bit input is an address for a ROM location containing the SET-UP information for each rate. Table 4-3-1 lists the baud rate generator divisors.

E60 was originally designed to operate with a crystal as a self-contained crystal controlled oscillator and divider. The oscillator is located elsewhere, so the oscillator inputs EXT1 and EXT2 receive the microprocessor clock driven out of phase by two inverters in E38.

| (Input frequency = 2.76480 MHz) | |||

|---|---|---|---|

| X16 Baud Rate | Divisor | Output | Freq (Hz) Error |

| 50 | 3456 | 800 | |

| 75 | 2304 | 1200 | |

| 110 | 1571 | 1760* | -0.006% |

| 134.5 | 1285 | 2152* | -0.019% |

| 150 | 1152 | 2400 | |

| 200 | 864 | 3200 | |

| 300 | 576 | 4000 | |

| 600 | 288 | 9600 | |

| 1200 | 144 | 19200 | |

| 1800 | 96 | 28800 | |

| 2000 | 86 | 32000* | +0.465% |

| 2400 | 72 | 38400 | |

| 3600 | 48 | 57600 | |

| 4800 | 36 | 76800 | |

| 9600 | 18 | 153600 | |

| 1900 | 9 | 307200 | |

| * Output frequency shown is nominal value. Include percentage error to get actual frequency. | |||

The serial transmit and receive interfaces are ICs that convert between TTL signals and EIA RS-232-C unbalanced bipolar signals. The electrical specifications and connector pinouts are described in Chapter 3, Installation.

Certain pins on the PUSART are labeled with standard modem control designations. These pins are readable [Data Set Ready (DSR)] or writable [Data Terminal Ready (DTR)] and [Request to Send (RTS)] as buffered bits in the PUSART’s status and control bytes. Other signals from the modem pass through EIA level translators with Schmitt trigger inputs to a tristate buffer which, when enabled by the MODEM RD command, presents them to the data bus. Another signal [Speed Select (SPDS)] is written from the data bus into the NVR latch which is a convenient extra latch position. None of these signals are used to support modem control in the basic VT100. They are always programmed at power-up to allow normal full duplex operation with some modems when a standard EIA cable is installed between the modem and the VT100. See Chapter 3 for more interface information.

Three kinds of data can be exchanged between the VT100 and the host: control characters, control functions, and displayable characters.

Control characters are any ASCII characters in the range 0 - 1FH. They include carriage return and line feed.

Control functions start with a control character (escape) and contain additional characters which extend the range of special actions that the terminal can perform. Cursor home is such an action. Some control functions can contain numeric parameters to modify the special actions. Direct cursor addressing is a typical example. Appendix A of this manual describes the programming and use of the control characters and functions in detail.

Displayable characters are those ASCII codes that are stored in the screen RAM, causing a character to be displayed on the screen.

The microprocessor checks each character as it comes in from the PUSART. Only four characters cause any special action at this time. Control codes XON and XOFF (see below) are immediately processed while NULL and DELETE are discarded. Everything else gets put in a 64 character (128 characters in later model terminals) first-in/first-out space in the scratch area of RAM called the SILO. The SILO processor routine maintains this area by updating two locations called SILIN and SILOUT. These point to the current entry and exit points in a loop of memory locations. The farther apart they are, the more characters are in the SILO. The addresses of the two points are subtracted from each other to determine the filling of the SILO. The subtraction is performed in modulo 64 (or 128) arithmetic to accommodate the rotation of the locations.

The SILO is necessary because when the microprocessor reads a character, it acts on that character completely before taking another one. For example, a line feed character causes the processing needed to accomplish a scroll. The processing time often exceeds the time between characters at the port. To save the characters that might arrive and get lost during a special action, the microprocessor responds to the received data interrupt by quickly moving the data to the SILO. Only the examination described above gets performed. After the current action is finished, the microprocessor gets the longest waiting character out of the SILO and range checks it. If it is less than 20H, it is a control character and the microprocessor processes it. If it is 20H or above, the microprocessor puts it in the next character position in the screen RAM.

XON and XOFF are two control codes that the terminal and host may send to each other to control the pace of data transmission. The host usually has a buffer space similar in function to the VT100’s SILO. If either device has a large processing load at the same time that a lot of data is being received, the buffer or SILO can fill up. The receiving device monitors its buffer and sends Transmit Off (XOFF) when the buffer contains a predetermined number of characters. On the VT100 this value is 32 characters. (A second XOFF is sent at 112 characters in late model VT100s.) The sending device should stop transmitting until it receives Transmit On (XON). When the receiving device empties its buffer to another predetermined number of characters (16 characters on the VT100), it sends XON.

The NO SCROLL key on the keyboard enables and disables SILO fetching. If data continues to arrive, the SILO management routine sends XOFF or XON as required. The microprocessor keeps track of the current state and sends the opposite command the next time the key is pressed. CTRL-S and CTRL-Q send XOFF and XON directly. Coordination of various causes of XON and XOFF is discussed in Appendix A.

Because of the serial interface, several character times may elapse before the transmitter acts on XOFF and its last character passes through the receiver. This partly determines how full the buffer can be before XOFF must be sent. The other determinant is the worst case condition in split speed operation. If the terminal transmits at a low speed and receives at a high speed, the interface delay can allow several characters to arrive before XOFF stops their transmission. A detailed discussion of this problem is in Appendix A.

A parser is a routine that examines a sequence of characters. It then starts processes and extracts parameters based on the contents of the sequence. The term comes from the grammarian’s practice of parsing (separating) a sentence into its component parts: subject, verb, object. The meanings of many sequences are being standardized throughout the data processing industry through American Standards Institute (ANSI) and International Organization of Standardization (ISO) committees. The VT100 employs a subset of several of these standards, plus it has several private sequences to allow it to perform certain DEC-specific functions like behaving as a VT52.

A character in the range below 20H is always the starting flag for the parsing process. Some functions have only the first character for their sequence; line feed (0AH) is an example. After the function is performed, the next character is taken from the SILO. If it is not in the control range, it is put on the screen. Escape (1BH) is the flag for a longer sequence. After escape, characters are taken from the SILO and range-checked as intermediate (20H to 2FH) or final (30H to 7EH) until a final character appears. The sequence is interpreted and the appropriate function performed. Then the next character is taken from the SILO and displayed if not in the control range. If a sequence is not supported by the VT100, it is parsed and then ignored.

Detailed descriptions of the functions are in the VT100 User Guide and in Appendix A of this manual.

In local mode, keyboard output bypasses the communication transmitter and receiver and SILO and is acted on directly. The Data Terminal Ready signal (DTR) at the EIA interface is unasserted in local.

The standard terminal port (STP) is a printed circuit board edge connector on the basic video board that contains twenty pairs of contacts. When no board is plugged into the connector, the pairs of contacts meet. All EIA data and modem control signals plus the two baud clocks pass through this connector. Future options may utilize the signals present at this connector. For a complete discussion of the details of the STP, see the STP Option Interface Guide, Chapter 7.

The VT100 can test its communication circuits, but because the operator must temporarily plug in a specially wired loopback connector, the test is not performed automatically. Refer to the Service chapter for instructions. There are two tests. One is a data test for either 20 mA current loop or EIA interfaces. This test transmits a pattern of data out the transmit line and examines the data as it returns through the receive line. Each bit of the data bus is tested with the eight test characters: 01H, 02H, 04H, 08H, 10H, 20H, 40H, 80H. This group of eight passes through the circuit repeatedly while the microprocessor changes the baud rate after each pass.

The second test, for EIA only, tests the modem control lines to ensure that they can be controlled. Some terminal controller modules have an etch revision at E39 that does not permit EIA testing. These modules can be recognized by the presence of extra wires attached at E39.

Table 4-3-2 lists the test connector wiring.

| From | To | |

|---|---|---|

| EIA: | Pin 2 | Pins 3 and 15 |

| Pin4 | Pins 5 and 8 | |

| Pin 20 | Pins 6 and 22 | |

| Pin 19 | Pins 12 and 17 | |

| 20mA: | Pin 1 | Pin 3 |

| Pin 2 | Pin 7 | |

| Pin 5 | Pin 8 |

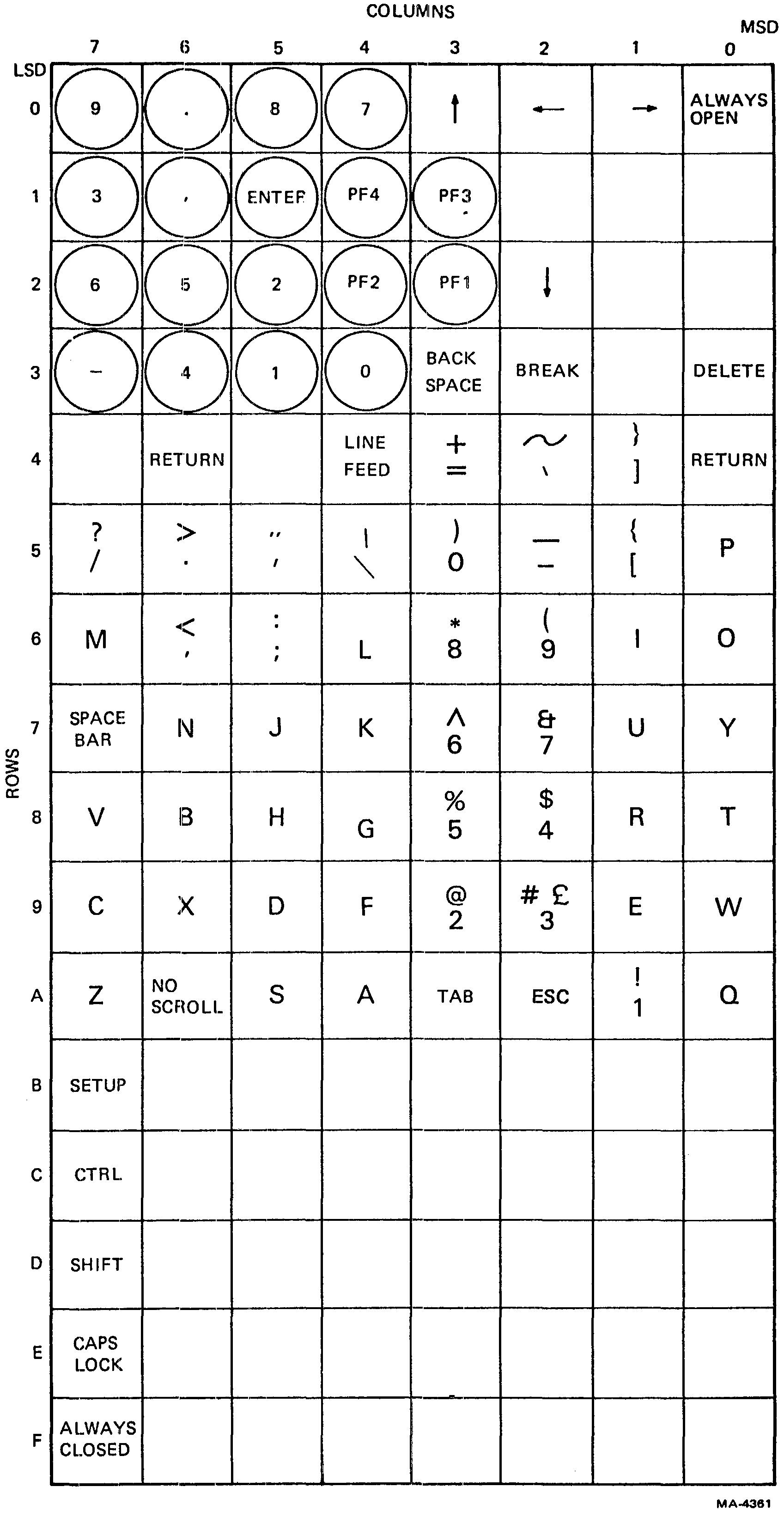

The VT100 keyboard is a typewriter-like array of momentary, normally-open switches. The array is mounted in a small case with a speaker for audio feedback and electronics for interfacing the array to the terminal. The VT100 keyboard connects to the terminal controller board through a three conductor cable that plugs into the back of the terminal cabinet. The cable carries power, ground, and a complex bidirectional data and clock signal. The terminal sends the clock signal and a status word that controls the LED indicators, the bell, and the keyboard scan process. The keyboard sends the row and column address of each key that is pressed. The terminal’s microprocessor then translates that address into an ASCII character and transmits it serially to the host through a UART or performs internal actions such as SET-UP and no-scroll. Refer to Section 4.3 for a discussion of UART principles.

This section describes the operation of the keyboard and its interface hardware and software in the terminal.

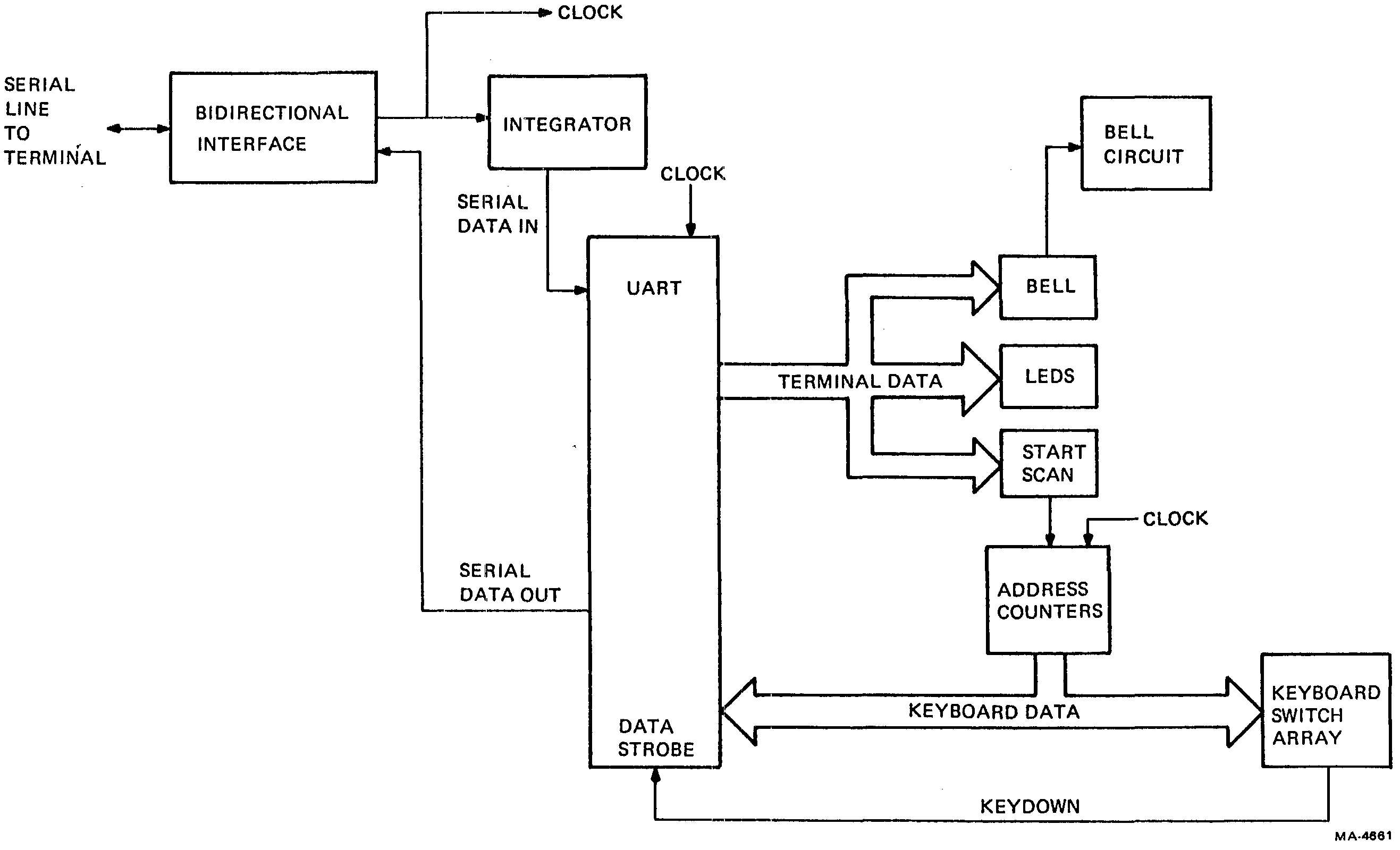

The bidirectional interface separates incoming from outgoing data on the single signal line. Incoming data from the terminal contains a clock that passes directly to the UART and the address counter circuit. Then the data and clock are integrated. The duty cycle encoded data becomes serial data. The UART deserializes the terminal data and produces an 8-bit parallel output. These bits control the bell and LEDs, and start address scanning, depending on which bits were set by the terminal in the keyboard status byte.

The address counters start on command and send row and column addresses to the keyboard switch array. When an address matches a key that is down, the Key Down signal strobes that address into the UART. The UART serializes the address and the bidirectional interface sends it to the terminal.

Information is exchanged between the terminal and the keyboard in serial form. One start bit, eight data bits, and one stop bit are transmitted using a clock derived from the horizontal timing circuits in the terminal. Besides timing the serialization of data in the terminal, the clock is also transmitted to the keyboard to time its circuits. The terminal data is a status byte that controls the keyboard by commanding key scans and other functions.

The keyboard transmits its data in the same format and with the same clock. Its data are the addresses of whatever keys are down during a scan. The last key address sent has the highest address possible and is always sent to indicate to the microprocessor that the scan is complete.

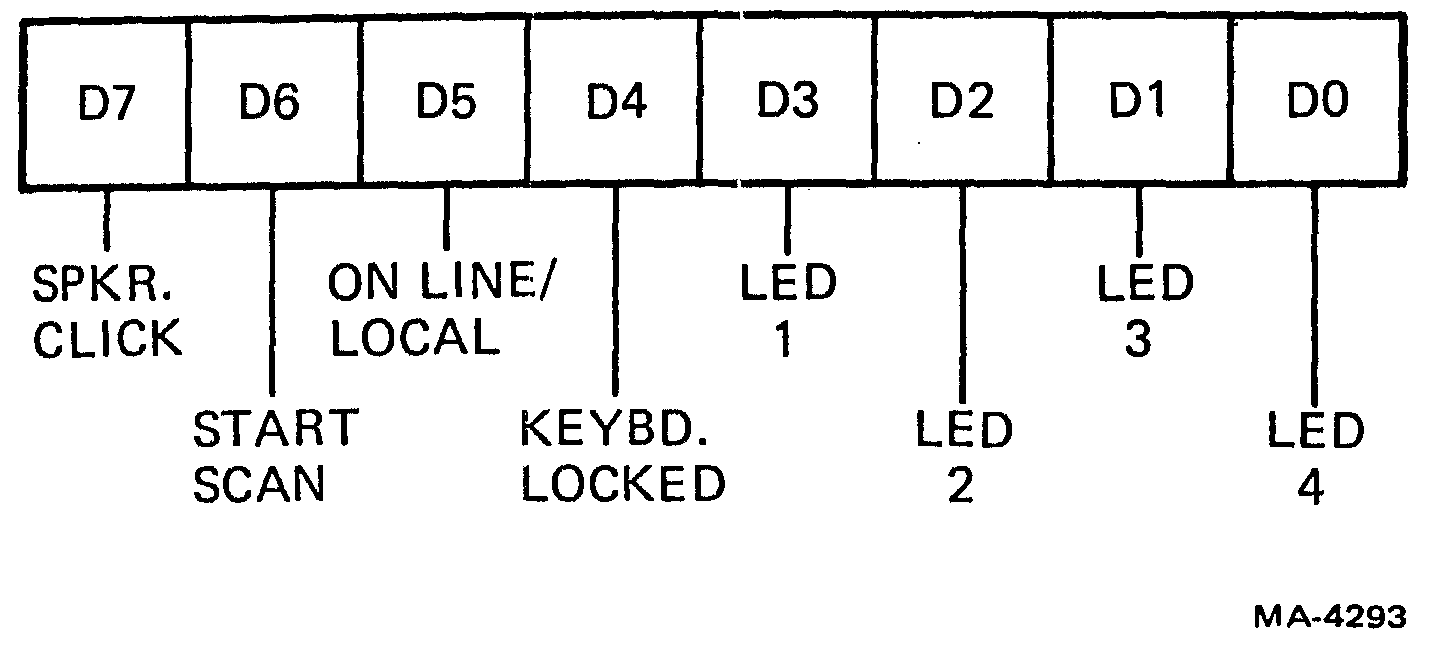

The terminal controls the keyboard through a status byte that it sends through the interface along with the keyboard clock. The first six bits of the 8-bit byte (Figure 4-4-2) control the On-Line/Local, Keyboard Locked, and four user programmable LEDs on the keyboard. Every time the status byte is sent, it refreshes the LEDs even if no new action is being taken. The seventh bit is sent only once in a vertical interval and initiates the scanning process in the keyboard. The eighth bit, if sent only once, causes the keyboard speaker to click. (Keyclick is defeatable at SET-UP.) If the bit is sent approximately two hundred times in a row, for about a quarter second, it sounds a bell.

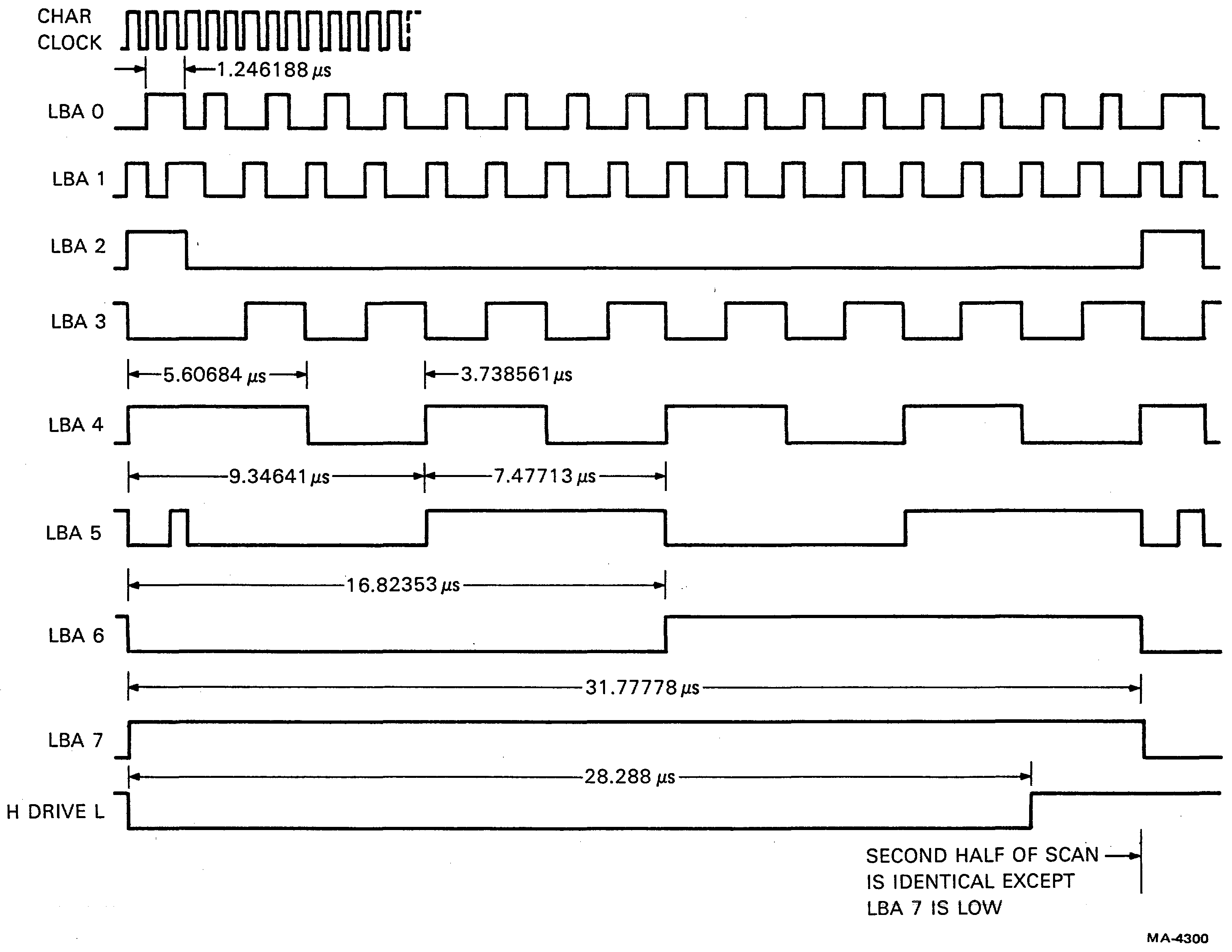

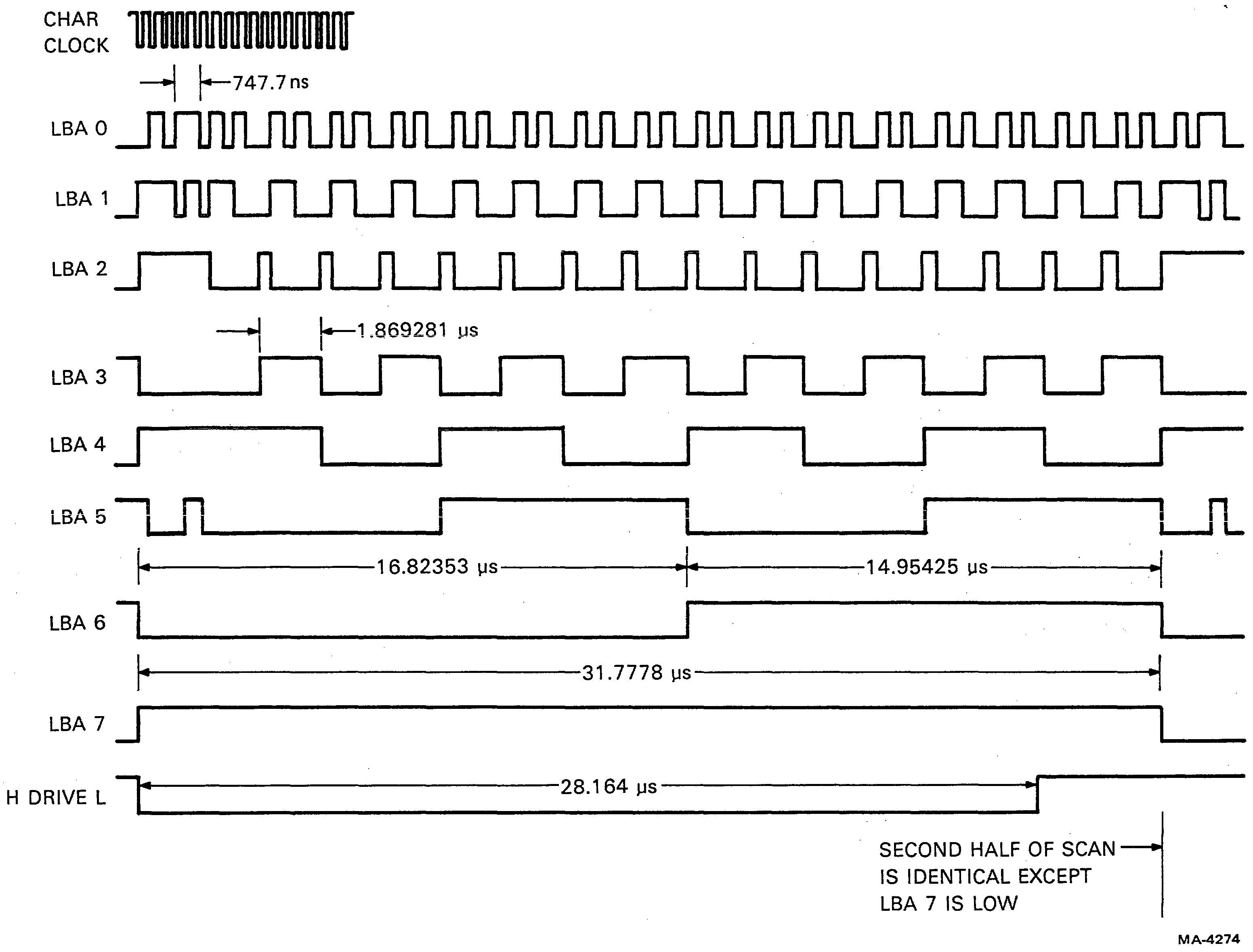

The operating clock for the keyboard interface comes from an address line in the video processor (LBA4). This signal has an average period of 7.945 microseconds. Each data byte is transmitted with one start bit and one stop bit, and each bit lasts 16 clock periods. The total time for each data byte is 160 times 7.945 or 1.27 milliseconds. Each time the Transmit Buffer Empty flag on the terminal’s UART gets set (when the current byte is being transmitted), the microprocessor loads another byte into the transmit buffer. In this way, the stream of status bytes to the keyboard is continuous.

Keyboard addresses are outputs from a counter that correspond to locations in a keyswitch matrix. The counter can address all locations in the matrix. If a keyswitch is closed, the counter output addressing that location is transmitted. The address counter is a pair of 4-bit binary counters arranged so that only the top seven bits go to the switch matrix. These outputs also connect directly to the UART transmit data inputs. The output of the first bit in the counter is a squarewave with a period equal to the amount of time that each key is sampled during a scan. Key Down L appears at the input to flip-flop E6 when the counter reaches the address of a key that is pressed. Half a sample period later, the first counter bit clocks the Key Down signal through flip-flop E6. The half period delay allows any glitches in the address counter to settle before Key Down asserts Data Strobe. Data Strobe loads the UART transmit buffer with the address count present at the data input at that moment. That address count represents the key that was down when Key Down was asserted.

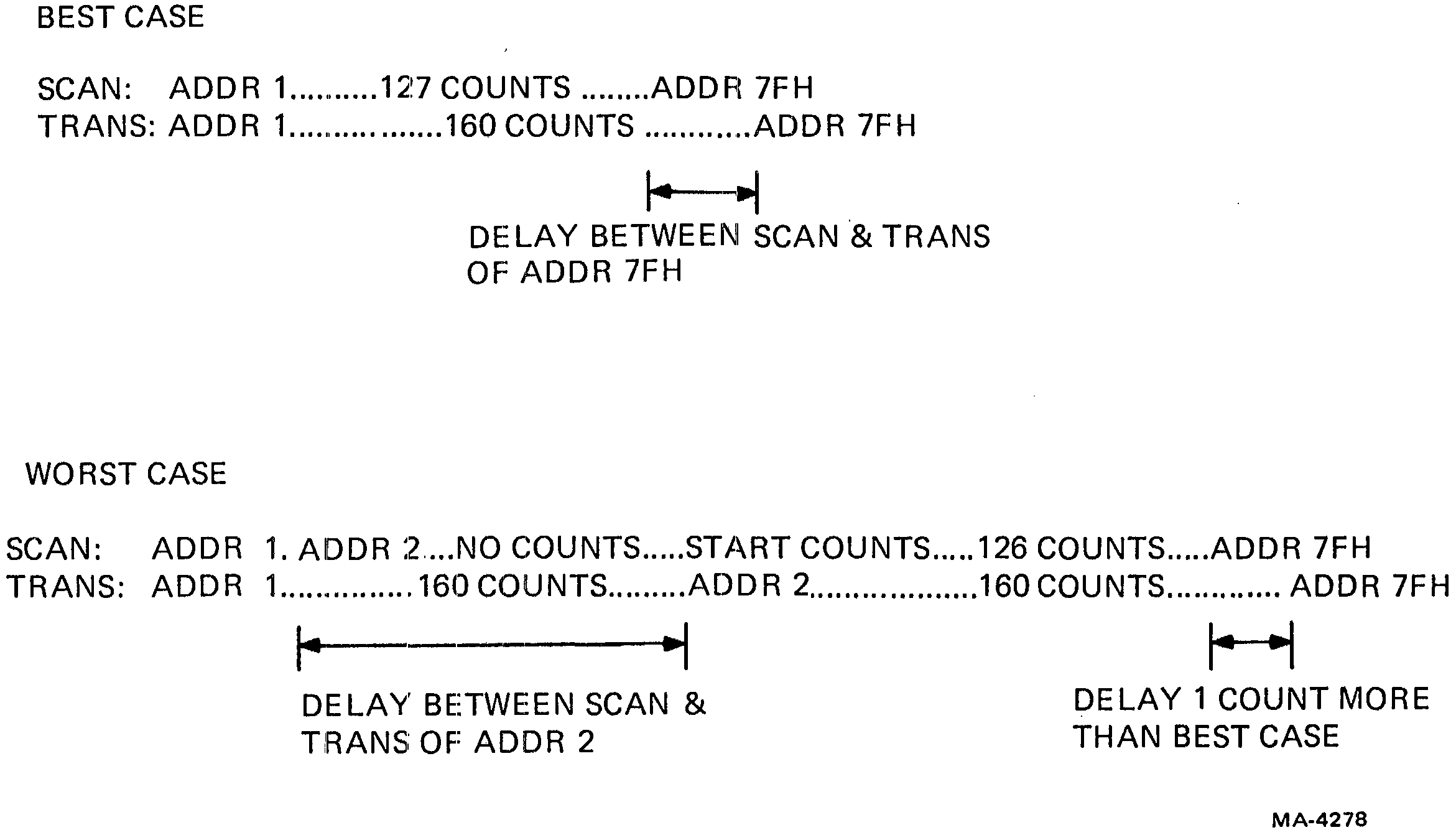

The UART, which is double-buffered, deasserts Transmit Buffer Empty while the transmit (outer) buffer is full. This stops the counter by blocking the clock at gate E4. As soon as the data moves into the inner shifting register, the transmit buffer empties, TBMT is asserted, and the count continues. In this way, any number of key addresses can be sent to the terminal. The time the scan takes to finish varies with the number of keys down. On the first address load, when transfer from the transmit buffer into the shifting register is immediate, the UART reasserts TBMT almost immediately. For loads later in the scan, the UART deasserts TBMT for a longer period because an address that loads into the transmit buffer must wait with the counter stopped until the previous transmission is done. Because the transmission time is 160 counts and the complete address scan takes only 128 counts, there is a minimum wait of 32 counts or about 20 percent of a character transmission time between the scan of address 7FH and the transmission of address 7FH if the first key in the scan was down. (Refer to Figure 4-4-3.)

Because it is hard-wired, the highest address (7FH) always asserts Key Down and gets transmitted, indicating end of scan to the terminal. The highest bit also clocks flip-flop E3 which clears the counters and stops the count. This is the only way that the scan is terminated. The scan begins again when the terminal sends the Start Scan bit in the status byte to the keyboard. When the data arrives, the UART asserts its Data Available flag. On the next clock transition, flip-flop E6 passes a short, clock-synchronized Data Available pulse to gate E5, resetting the flag in the process. E5 combines the Data Available pulse with the Start Scan bit if present to clear E3, allowing the count to begin.

After the terminal starts the scan, it waits for the 7FH address and then for a vertical interrupt (a synchronizing signal explained in VIDEO) before it will start the scan again. If there are a lot of keys down, the scan may take more than one vertical interval to finish. The keyboard ignores further requests to scan until the current scan is complete.

Here is a formula that estimates the delay between the time that the terminal asserts the start scan bit at its UART and the time that the terminal UART asserts data available upon receiving the final address 7FH. The clock driving the address counter and UART has a period of 7.945 microseconds, there is the number of addresses to the first closed key to be counted, and the serial transmission of an address takes 160 clock periods (16 clocks per bit, 8 data bits, 1 start and 1 stop bit).

| 160 | start scan command word to keyboard | ||

| + | m | counts to first key | |

| + | n × | 160 | for n keys down |

| + | 160 | transmission of 7FH | |

| Total × 7.945 = microseconds | |||

For example, suppose that one key, #24, is down.

| 160 | start scan command word to keyboard | ||

| + | 24 | counts | |

| + | 160 | transmission of key #24 address | |

| + | 160 | transmission of 7FH | |

| 504 × 7.945 = 4004 microseconds (4.0 µs) [TYPO?] | |||

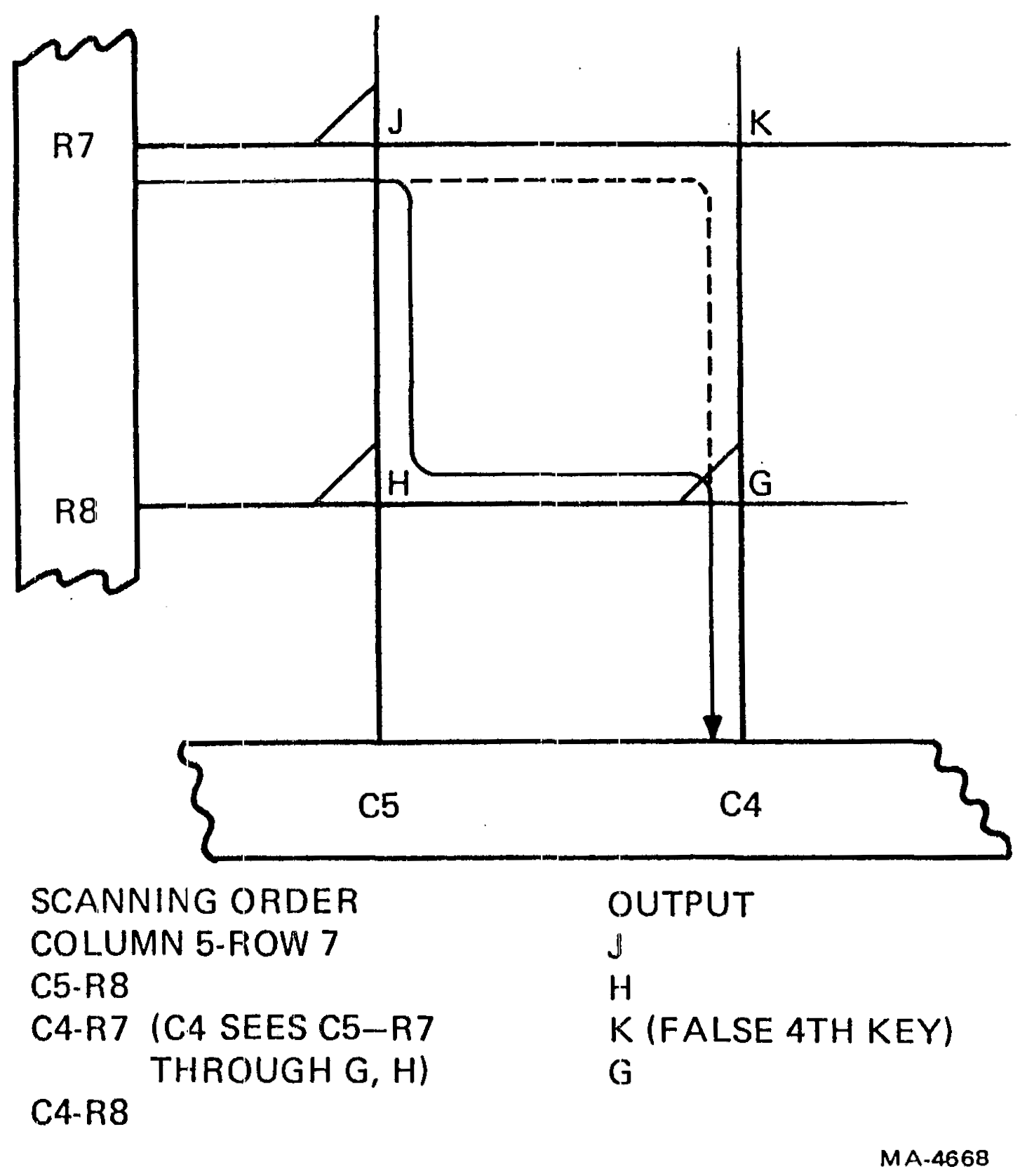

The keyboard is an array of contact pairs arranged in 16 rows and 8 columns (Figure 4-4-4). One side of each pair is connected to all the others in its column and each column connects to +5 volts through a resistor. Each of the eight columns also connects to an input on the eight-to-one multiplexer E14. The other side of each contact pair connects to all the others in its row and to an output on one of the one-to-eight demultiplexers E11 and E13. The seven outputs of the keyboard scan counter control the multiplexer and demultiplexers. The rows are selected by the lower four bits and the columns by the upper three.

A low input to the selected column line on the multiplexer causes a Key Down L signal. If a key is pressed when the row and column address is not on its position, the unselected demultiplexer line is high and there is no change in level across the contacts. If the demultiplexer line is selected, it is low, and the closed contact pulls the column low through the resistor. Each column is scanned top to bottom as the low four address lines count; then the next column is selected and scanned. The complete keyboard scan takes about 1 millisecond when no keys are down.

The last row and column position (address 7FH) is wired to always indicate key down. This value indicates to the terminal that the scan is ended.

The terminal sends data and clock to the keyboard; the keyboard sends data only. Transmission is asynchronous, full duplex, serial, 8-bit data with one start bit and one stop bit over a single signal line. Four states can exist on the line, representing the two signal states from each end of the line.

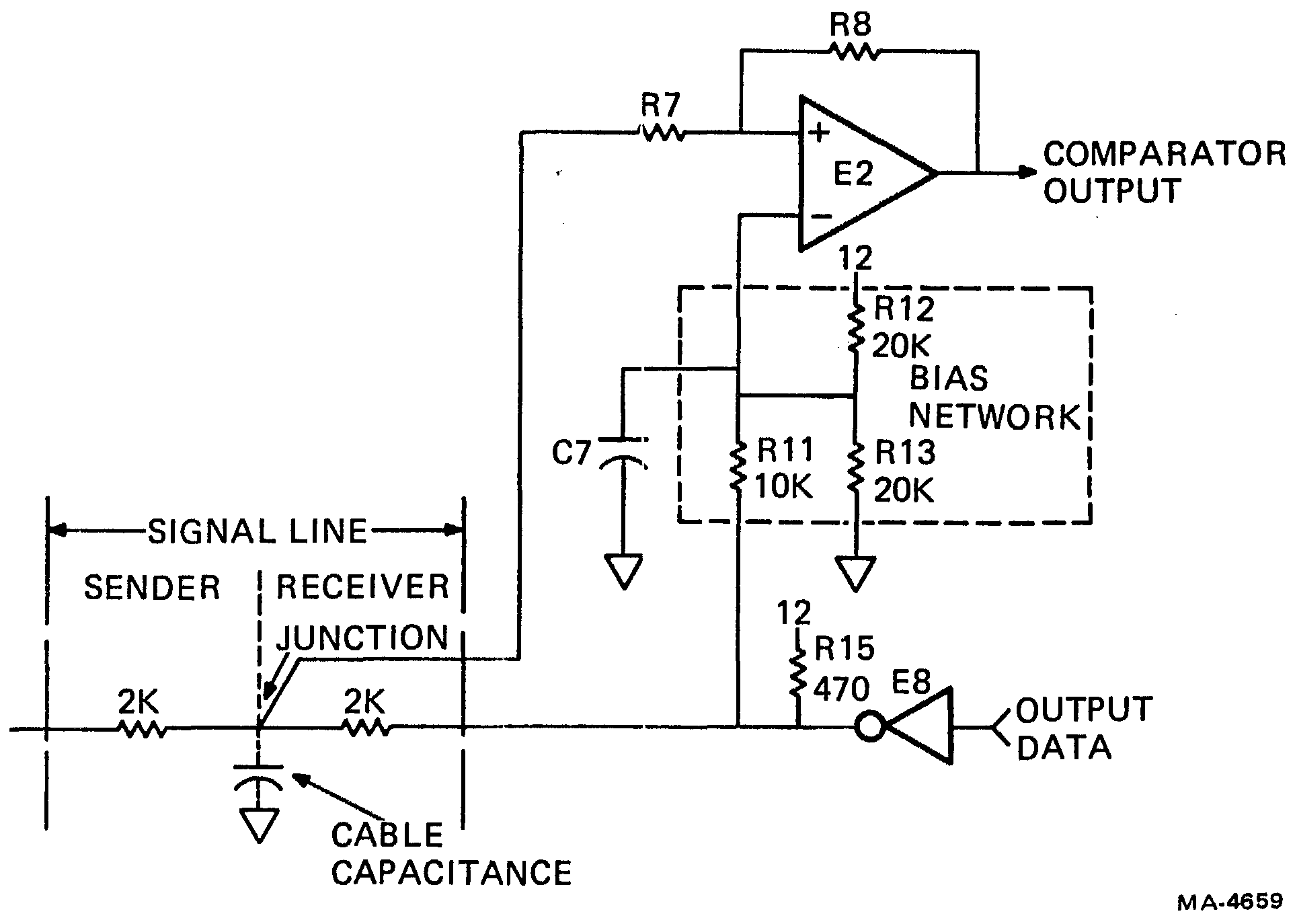

Both signals may coexist on the same wire, originate at opposite ends, and simultaneously communicate provided that sensing resistors are put at each end. The interface works by observing the voltage variations on its input (across the sensing resistor) while biasing the input in an opposite direction with its own output signals so that only input variations can cause enough change to exceed the threshold of detection.

Refer to the keyboard interface schematic, Figure 4-4-5a. If one side of the line is at +12 volts and the other is at ground, then by Ohm’s Law, the center of the two equal resistors will be at V/2 = 6 volts. If both sides are at 0 or 12, the center will be identically at 0 or 12. Thus the signal line can either have no current flow but with the junction of the two resistors at either 0 or 12 volts, or the junction can be at 6 volts with current flow to the left or to the right, thereby representing the four required states.

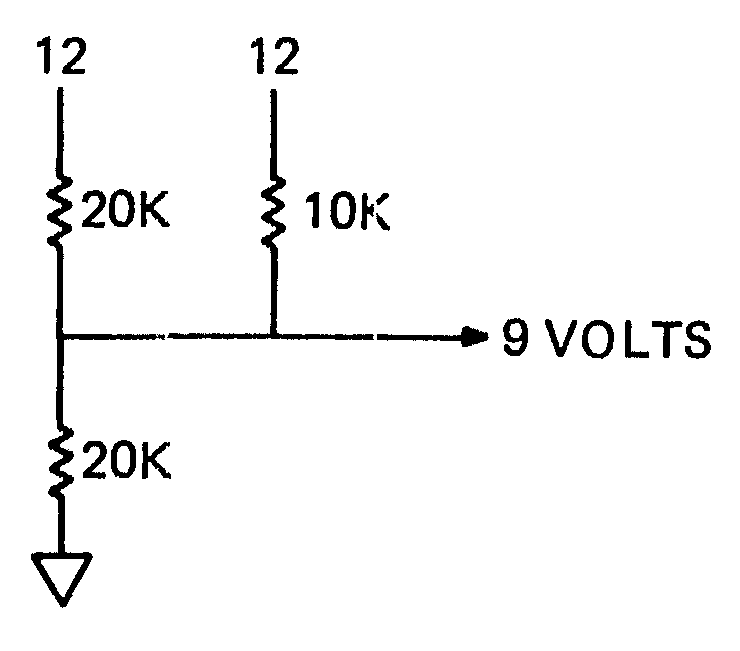

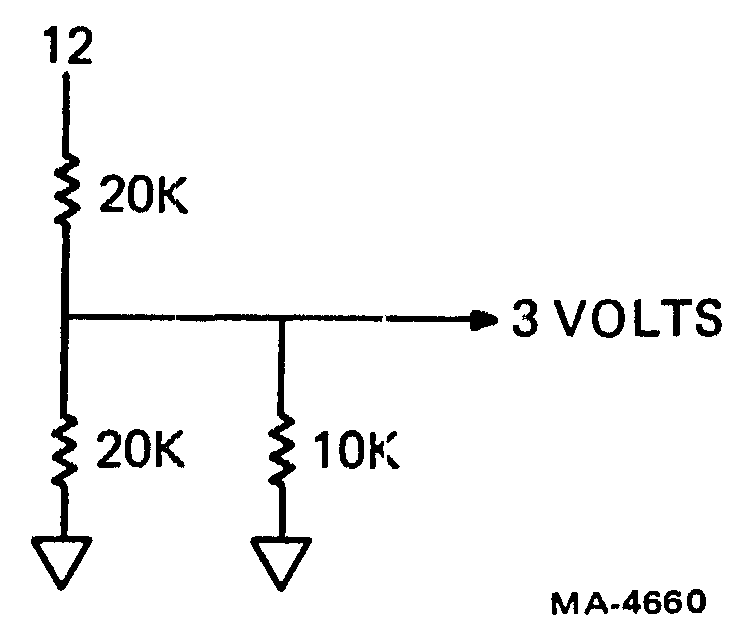

The receiving side of the keyboard interface separates the incoming signal from its own output by delivering a sample of its output to the inverting input of a comparator. Refer back to Figure 4-4-5. This provides an additional input for the comparator which compensates for the variation that occurs on the noninverting input at the same time that the output changes. R12 and R13 (both approximately 20K) and R11 (10K) are a divider providing bias to the comparator. If E8 (an open collector driver) is off (high), then the end of R11 connected to E8 is essentially at +12 volts through R15 (470). The R11, R12, R13 divider outputs 9 volts as shown in Figure 4-4-5b. If E8 is on (low), the end of R11 is at ground, and the divider outputs 3 volts (Figure 4-4-5c).

Meanwhile, the signal from the other end of the signal line is admitted to the noninverting input of the comparator through a resistor (R7) whose value is small compared to the comparator’s high input impedance. The positive feedback resistor R8 provides a small amount of hysteresis to improve the circuit’s noise immunity.

For the case where the junction is at 12 volts, there is no ambiguity about what signal the sender is sending. The comparator must produce a high output because the sender is outputting a high level. (The receiver is also sending a high level but no distinction between the two needs to be made.) The bias network presents a 9 volt signal to the inverting input, so the comparator sees a +3 volt difference and goes high.

For the case where the junction between the sender and the receiver is at 0 volts, there is again no ambiguity. The comparator must produce a low output because both sender and receiver are outputting low levels. The bias network presents a 3 volt signal to the inverting input, so the comparator sees a -3 volt difference and goes low.

For the case where the junction is at 6 volts, either end could be the high or low sender. The decision is made at each end by each circuit examining its own output to decide whether it or the other end is sending a particular level. If the sending end is at 0, the noninverting input sees 6 volts. The receiving end is outputting 12 volts, and the network outputs 9 volts to the inverting input. The comparator sees a difference of -3 volts and outputs low in recognition of the low level at the sending end. If the sending end is at +12, the noninverting input sees 6 volts. The receiving end is outputting 0 volts, and the network outputs 3 volts to the inverting input. The comparator sees a difference of +3 volts and outputs high in recognition of the high level at the sending end.

Table 4-4-1 summarizes the effects of the various signals.

| Send. End | Rec. End | Non-Invert. Input (Junction) | Invert. Input | Difference | Output |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 3 | -3 | 0 |

| 0 | 12 | 6 | 9 | -3 | 0 |

| 12 | 0 | 6 | 3 | +3 | 5 |

| 12 | 12 | 12 | 9 | +3 | 5 |

C7 compensates the circuit for the capacitance of the cable. If C7 were not present, the output of the comparator would glitch when the output driver on the same end of the line changed state. This would be caused by the output signal propagating immediately to the inverting input of the comparator but being delayed (by the RC time constant of the line) to the noninverting input. C7 is chosen so that the time constant of the line is the same at both inputs. Because the resistance seen at the middle of the line is approximately 1000 ohms (two 2K resistors in parallel) and the resistance seen at the inverting input is approximately 5000 ohms (one 10K and two 20K resistors in parallel), C7 is about one-fifth of the cable capacitance. The value is not critical because the ratio of the two time constants can be as large as two and still provide acceptable noise immunity.

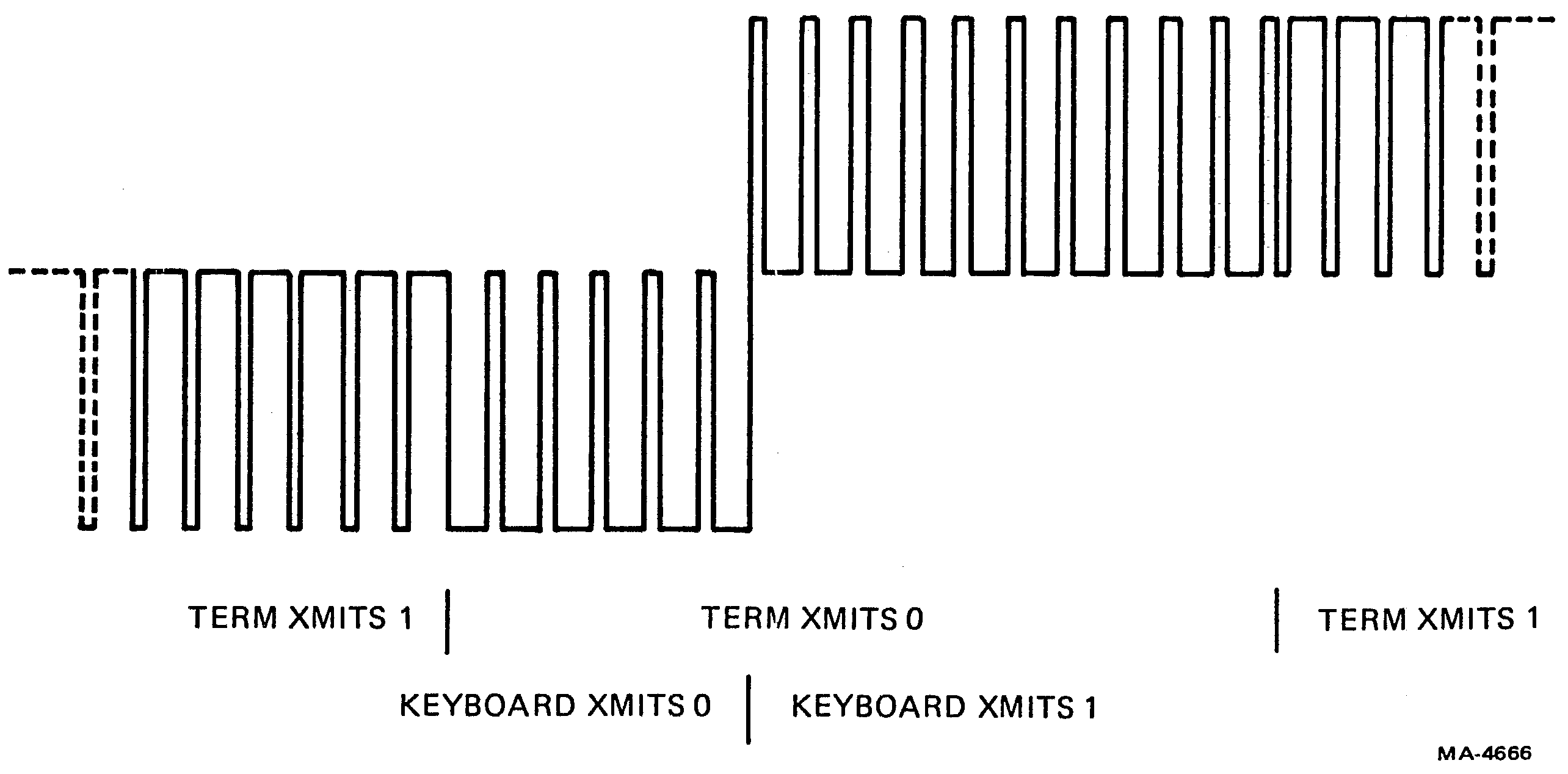

The keyboard requires a clock for its operation and is provided with one by the terminal controller side of the interface. To transmit a clock independently of data on the same wire, the terminal side of the interface generates a clock signal within which data is encoded as a pulse width modulation. The terminal circuit produces a 75 percent high pulse width output for the mark state. Data transmission causes the clock output to switch between 75 and 25 percent pulse width (duty cycle).

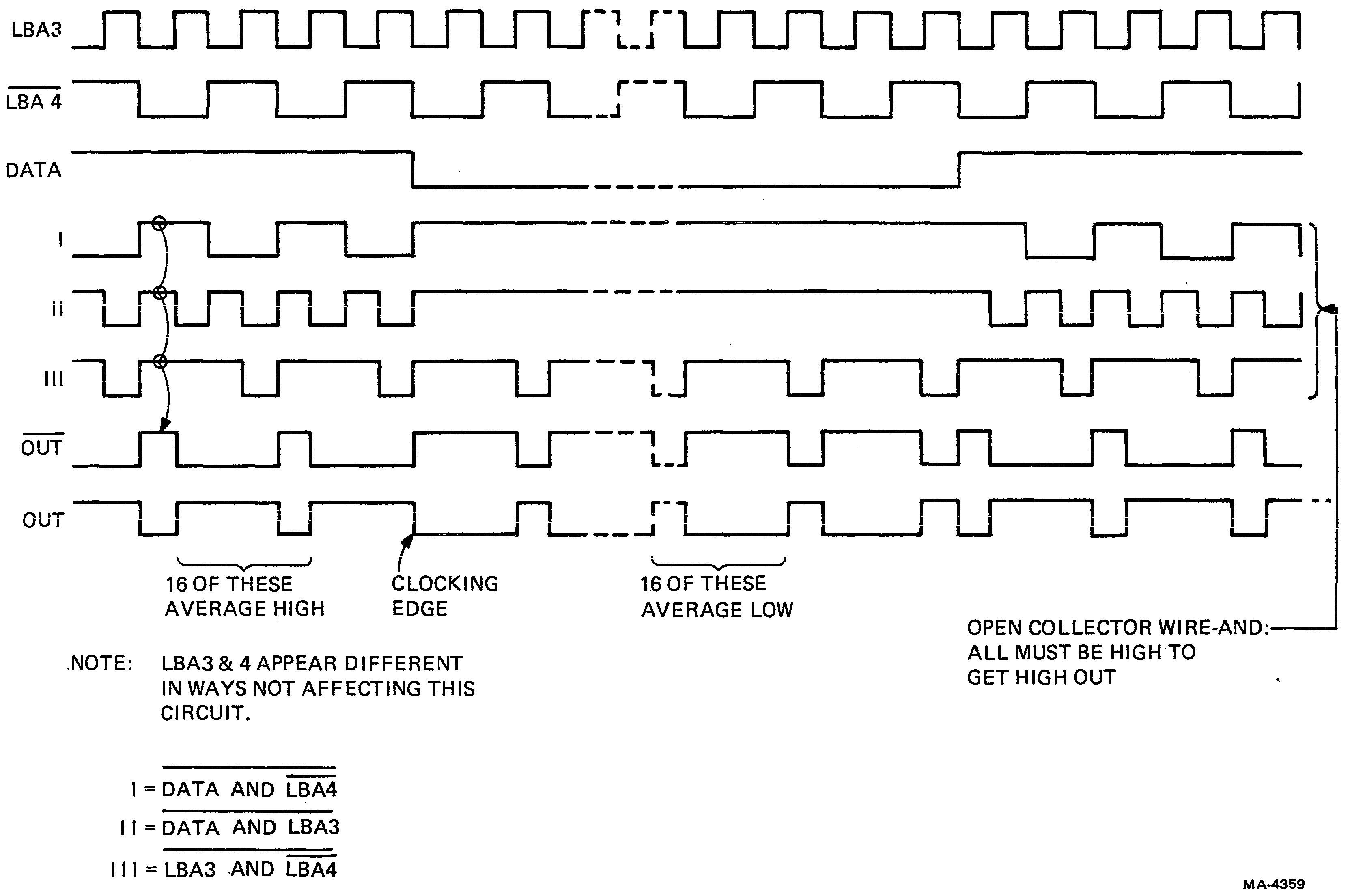

Figure 4-4-6 is a timing diagram that illustrates the formation of the pulse width modulation. Three nand gates, I, II, and III, combine three signals, Data, LBA 3, and inverted (not) LBA 4. The three gate outputs are wire-ANDed so that all three must have high outputs to produce a high to the out inverter, which drives the terminal’s end of the bidirectional interface. The timing is not precisely correct in this drawing because the LBA signals, addresses to the line buffer in the video processor, are not pure squarewaves and have variations in their periods (see the DC011 section). These variations give the keyboard signal the appearance of clustering in groups of four, but they do not affect the operation of the circuit.

The negative transition of each output pulse occurs at the clock interval regardless of the presence of data. This transition is therefore the reference point for the keyboard clock at the receiving end.

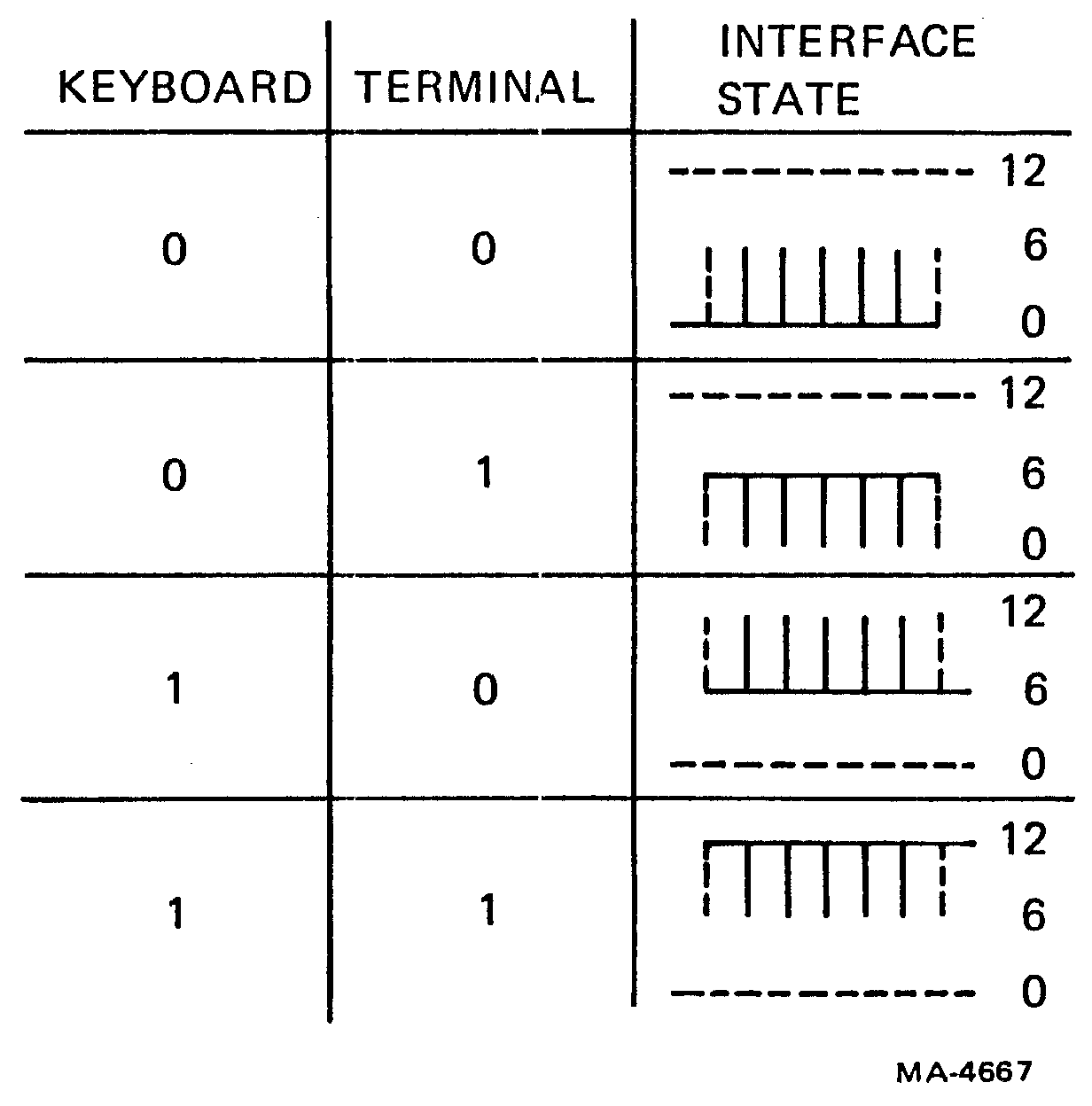

Figure 4-4-7 illustrates the four possible conditions on the interface line when the effect of the clock is included. Figure 4-4-8 shows all four states and the transitions between each of them. Two series sensing resistors in the interface circuit divide the signal in half at the wire. Therefore, although the drivers swing 12 volts at each end, the figures show only 6 volt variations.

The keyboard recovers the modulated clock signal sent by the terminal but must also separate the data from the clock. The signal is sent directly to the UART and address counter circuits as a clock. The negative edge of the clock occurs at a fixed interval while the positive edge varies according to the duty cycle modulation. The keyboard circuits use the negative edge and ignore the variable pulse width.

Data is extracted from the combined clock-data by a simple resistor-capacitor filter on one input to a comparator. The other comparator input is referred to one-half the power supply. Because the duty cycle of incoming data is either 1/4 or 3/4, the capacitor charges to that proportion of the supply voltage over the 16 clock periods of each bit. The comparator switches when the capacitor voltage rises or falls past the reference value. The short duty cycle of zeros averages to a low voltage that holds the comparator output low. The long duty cycle of ones averages to a high voltage and switches the comparator to a high state. The comparator output goes to the serial data input of the UART where it is deserialized. When all ten bits of a transmitted character are loaded into the UART, it asserts Data Available. This signal enables the bell and scan start if the appropriate bits were set in the byte. The LED bits remain latched at the parallel output of the UART until the next command byte arrives.

The keyboard UART serial output goes directly to an open collector driver that swings its end of the bidirectional signal line between 0 and +12 volts. This is shown as E8 and R15 in Figure 4-4-5a. The circuit is identical at both ends of the interface.

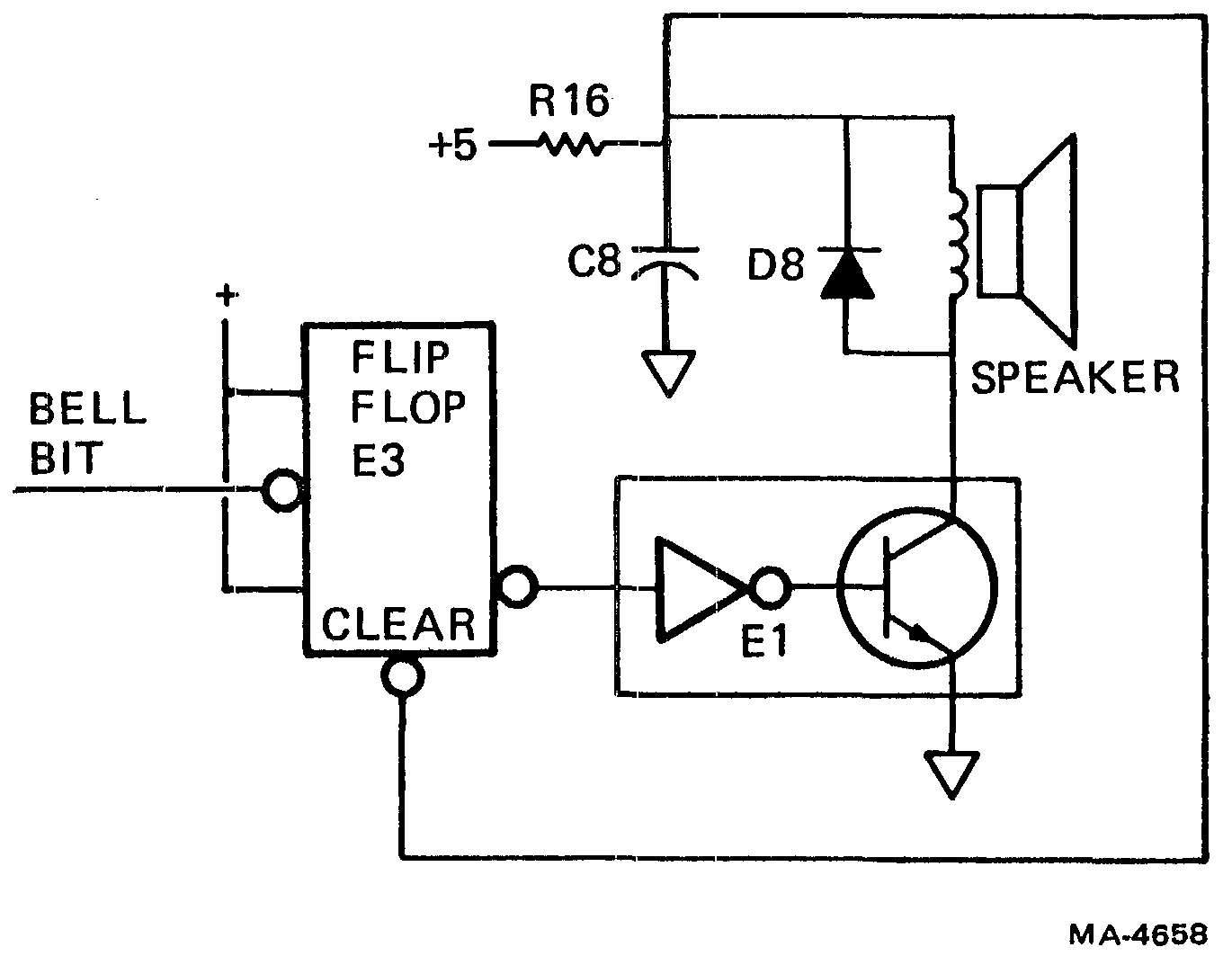

The keyclick/bell circuit provides audio feedback and attention signals for the user. A bit in the keyboard status word controls the bell. Refer to Figure 4-4-9 for the circuit. Capacitor C8 charges to +5 volts through resistor R16. The speaker connects between the capacitor and the collectors of the transistors in E1. When a single status word contains the bell bit, flip-flop E3 toggles and turns on E1. C8 discharges through the speaker and E1, generating a click. When the voltage on C8 falls low enough, it clears E3. E1 turns off and C8 charges up for the next click. The value of C8 is selected to determine the volume of the click. D8 protects the transistors from inductive spikes from the speaker.

If the bell bit is set for many words in succession, the UART latch holds the data output constant. A one clock period pulse from the Data Available flip-flop E6 gates the bell bit through E5 to form a clock to E3. As C8 discharges through the speaker and E1, E3 clears itself, turning E1 off. Then C8 charges up again until the next Data Available pulse clocks E3 on again to repeat the discharge cycle. C8 discharges fast enough so each Data Available pulse (which arrives every 1.28 ms) triggers a cycle, allowing the circuit to produce an 800 hertz tone. Bell is generated by setting the bell bit for 0.25 seconds (about 200 status words). Each cycle of the tone is at a reduced amplitude compared with the single keyclick because R16 is selected to limit C8’s charging rate. The overall effect of the tone burst on the ear is that of a beep.

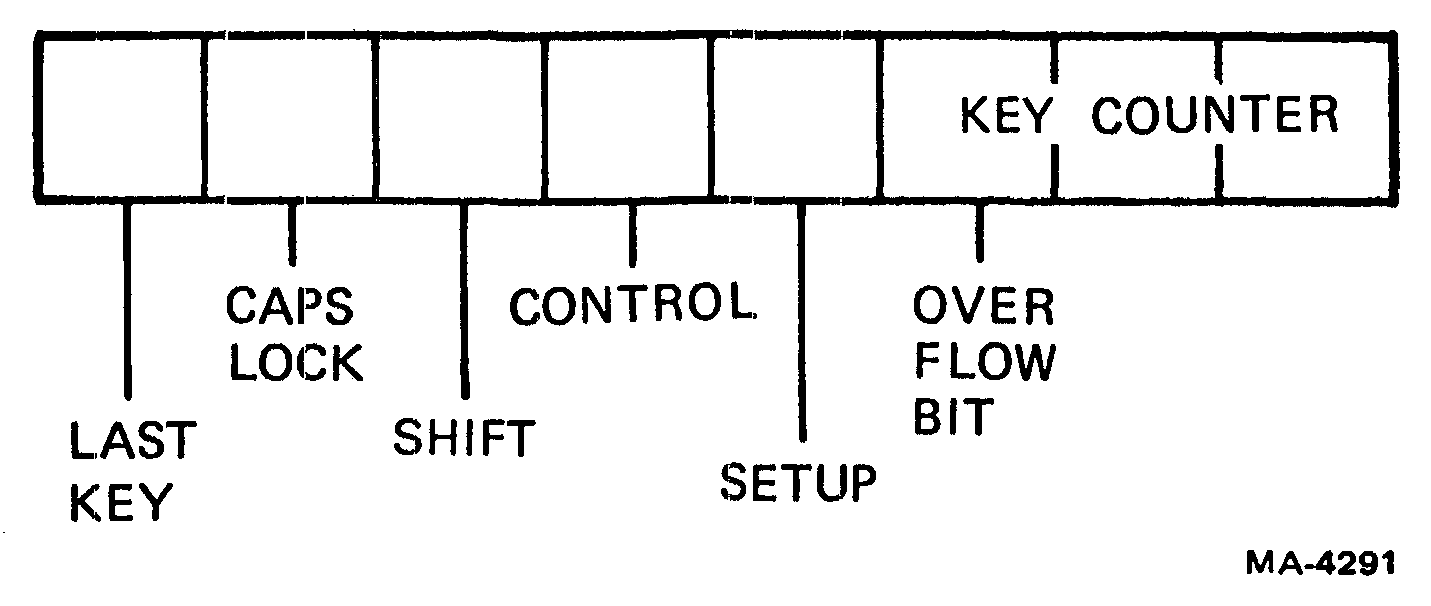

When the microprocessor responds to an interrupt from the keyboard UART and reads a key address from the UART data output, it immediately range tests the address. The function key addresses are all above the regular key addresses, with SET-UP the lowest at 7BH and the always down Last Key at 7FH. An incoming function key address causes a bit to be set in a flag byte called Keys (Figure 4-4-10).

When a key address below the function range arrives, the microprocessor checks the low three bits in Keys for the key count. If the count is less than three, the key address is stored in a three place New Key Address Buffer and the counter is incremented. If the count is already three, the counter is incremented but the key address is discarded.

The logical keyboard processor is that portion of the operating firmware that manages the interpretation and transmission of keyboard data. It consists of several processes.

For a key to be recognized as a new key, it must not have been down in the scan before entry is accepted. The microprocessor checks each key’s history at each scan. If a key was down during the last scan, it is old and is not entered. Only new keys, those not previously seen, are entered. This system allows a key to be held down without being continuously entered at each scan. (This process and auto repeat are discussed later.)

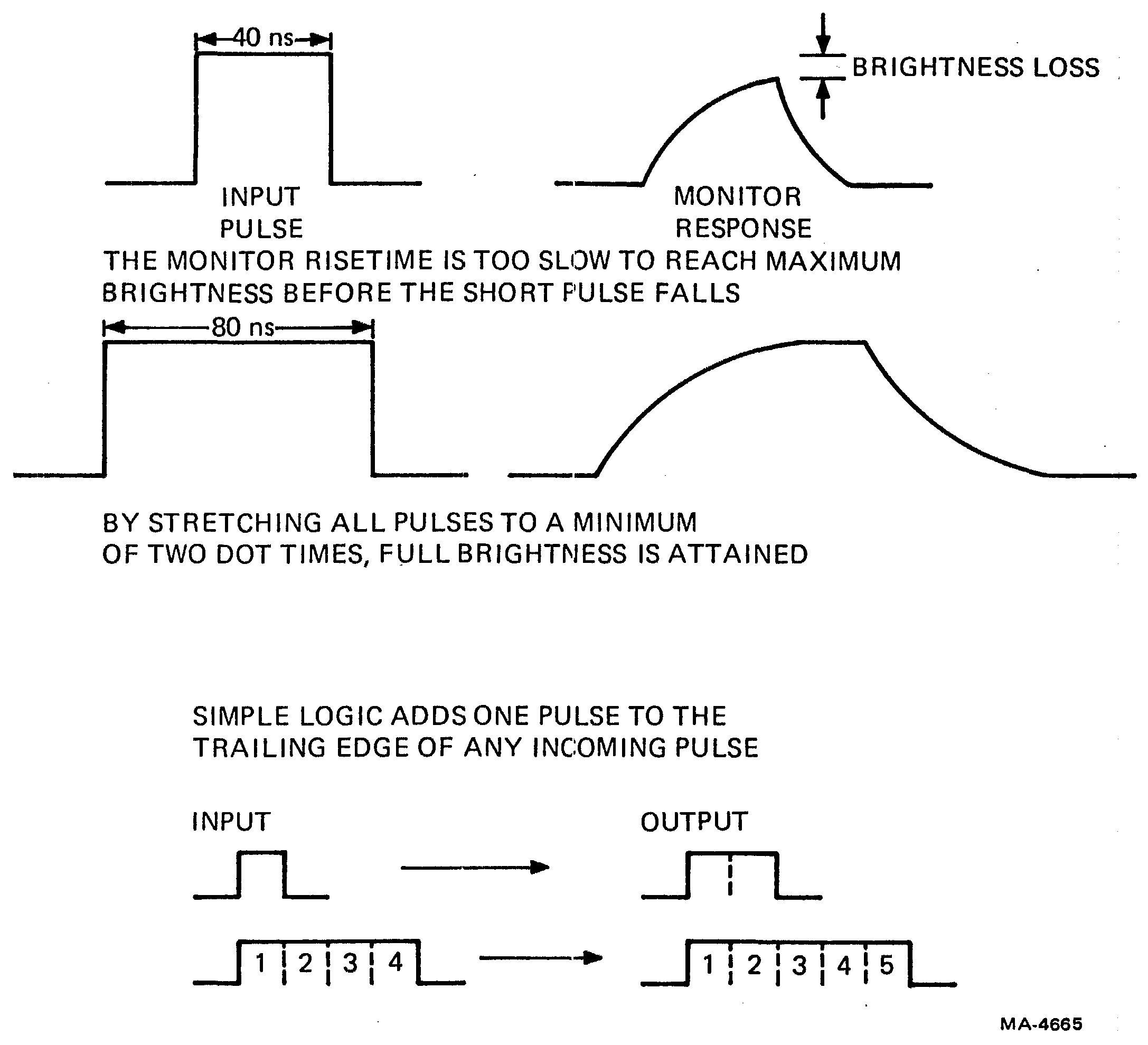

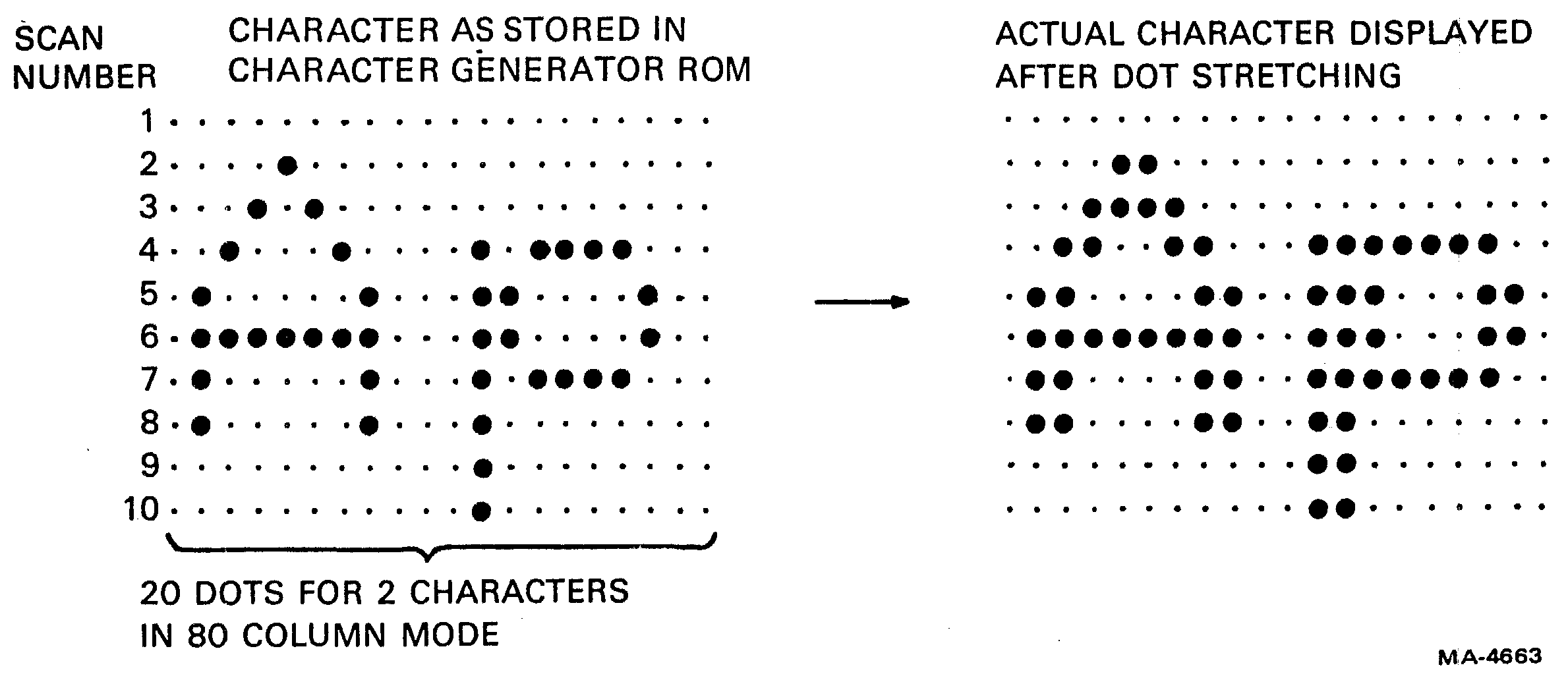

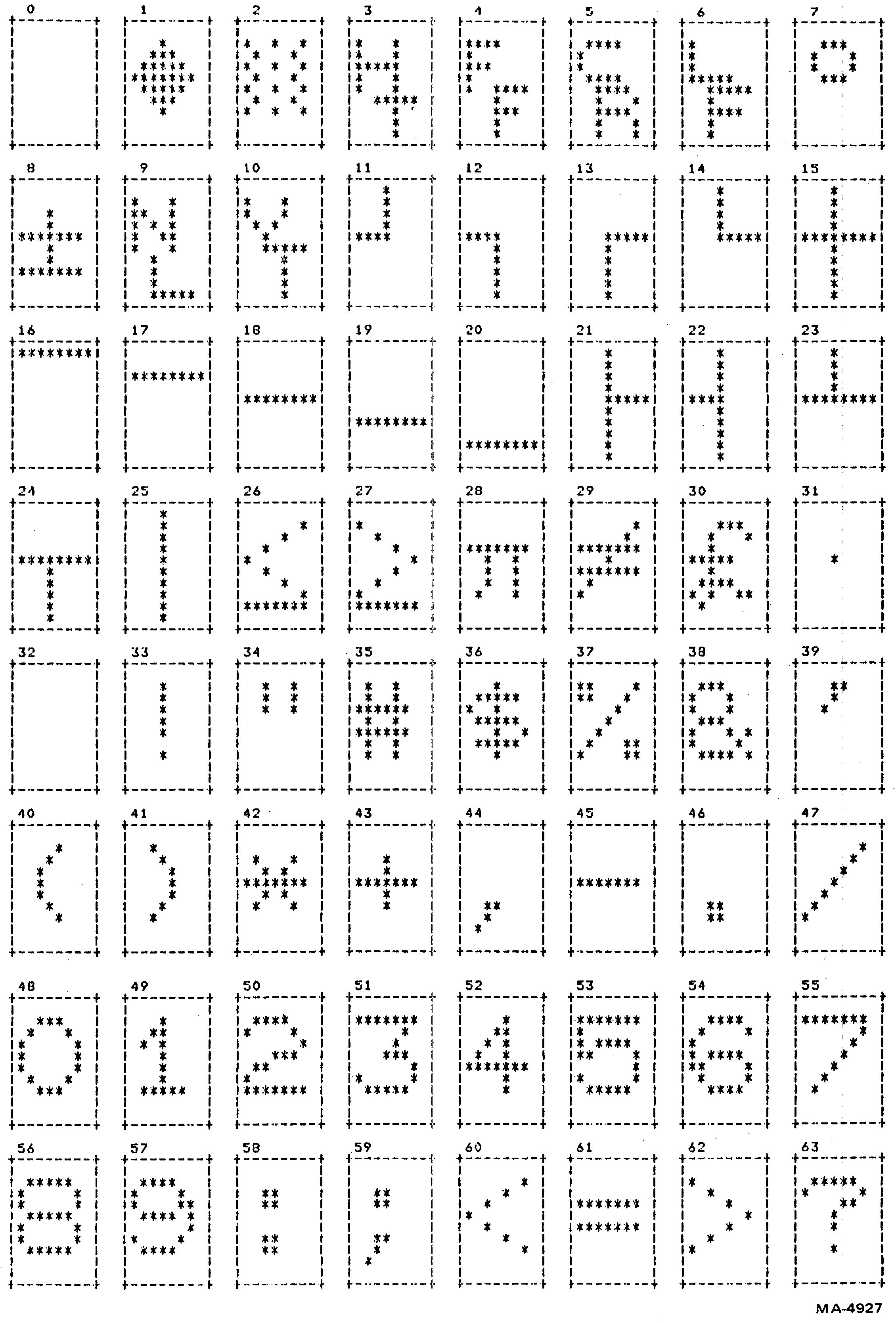

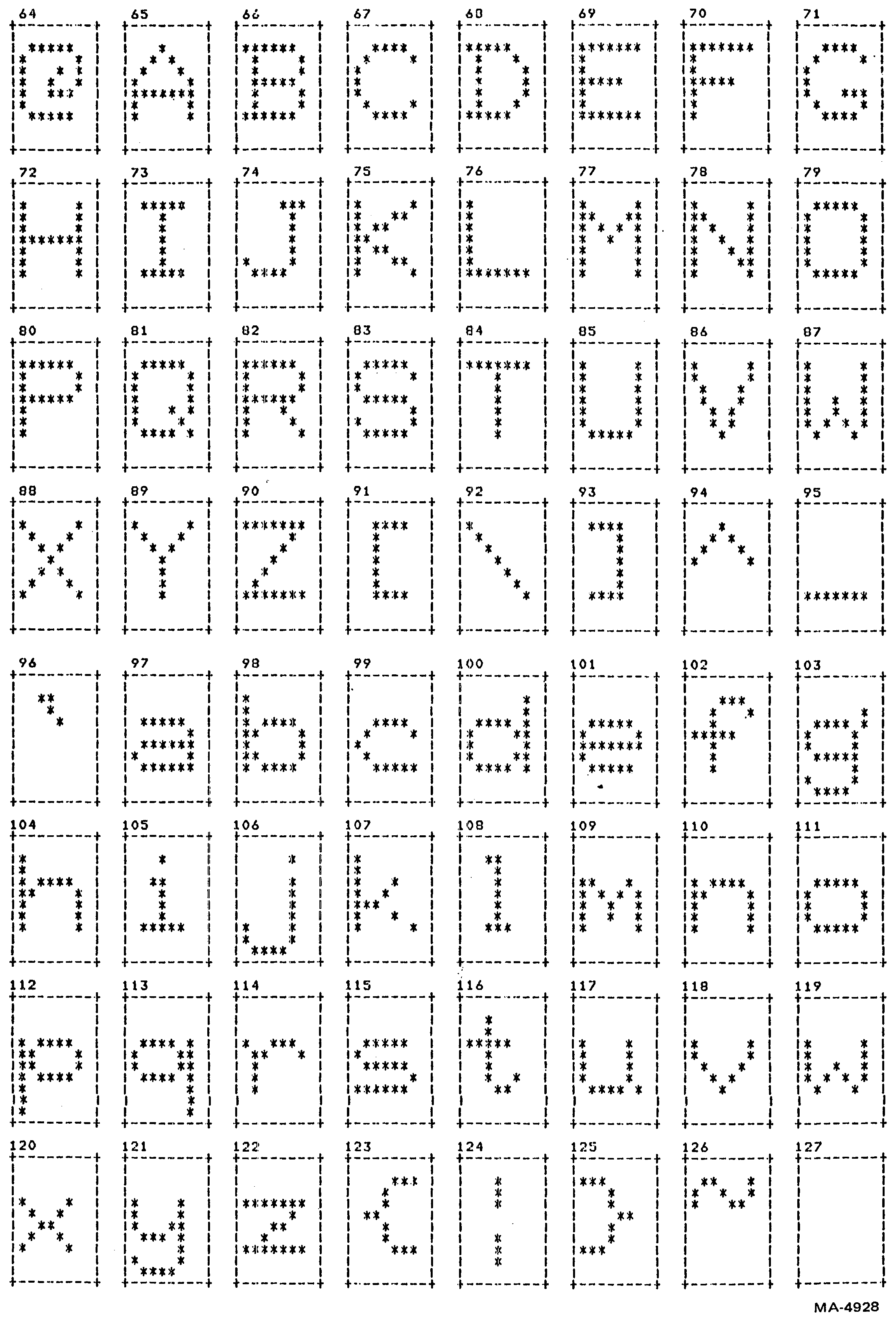

If a key is detected as down for the first time in a while, the microprocessor assumes that it has been pressed. During the scan when the key is first down, the contacts may bounce for several milliseconds. The time window when the contact is scanned is very short. If the contact happens to be bouncing open during that interval, it is not detected in that scan but the time between scans is long so it is finished bouncing by the next scan and is detected normally. If the contact happens to be closed for the first scan while still bouncing, it is detected. It is also detected on the next scan after it has stopped bouncing but now it is an old key and is not reentered.